# Mémoire De Magister En Micro-électronique

Thème:

# Etude Et Simulation Des Courants De Fuites Dans Les Transistors MOS A Canaux Courts

Présentée par : Mr ATTAR MOURAD

#### Soutenue devant le jury :

Mr GHAFFOUR Kheir-Eddine Professeur à l'université Président du jury.

Abou Bekr Belkaid .Tlemcen.

Mr BOUAZZA Benyounes Maitre de conférences à l'université Examinateur.

Abou Bekr Belkaid. Tlemcen.

Mr HAMDOUNE Abdelkader Maitre de conférences à l'université Examinateur.

Abou Bekr Belkaid. Tlemcen.

Mme BOUAZZA (née GUEN) Ahlam Maitre de conférences à l'université Encadreur

Abou Bekr Belkaid. Tlemcen.

## **Dédicace**

A ma mère, mon père A mes frères et sœurs A mes amies

#### Remerciements

A l'issue de cette thèse, je souhaite tout d'abord remercier ALLAH, qui m'a donné la force et le courage afin de réunir mes études et ma vie professionnelle.

C'est avec une profonde sincérité que j'adresse toute ma reconnaissance et ma gratitude à mon directeur de thèse, Mme Ahlam BOUAZZA (née GUEN), Maitre de conférences à l'université Abou Bekr Belkaid Tlemcen, avec qui j'ai eu plaisir à travailler, j'ai beaucoup appris à ses cotés, tant sur le plan scientifique qu'humain. Je tiens à la remercier pour la confiance qu'elle a su m'accorder en me proposant ce sujet de recherches et pour avoir contribuée activement à la réalisation de ce projet.

Je remercie vivement Mr GHAFFOUR Kheir-Eddine, Professeur à l'université Abou Bekr Belkaid Tlemcen, pour l'intérêt qu'il a porté à cette étude et pour m'avoir fait l'honneur de présider le jury de ma thèse.

J'exprime toute ma reconnaissance à Mr BOUAZZA Benyounes, Maitre de conférences à l'université Abou Bekr Belkaid Tlemcen et Mr HAMDOUNE Abdelkader, Maitre de conférences à l'université Abou Bekr Belkaid Tlemcen, d'avoir consacré leur temps pour me faire l'honneur d'en être les examinateurs de ce mémoire.

Enfin, tous mes remerciements à ma famille qui m'a supporté durant ces années de thèse et pendant tout mon parcours d'étude, et mes amis qui m'ont aussi bien soutenu pour franchir cette étape de mes études.

Sans oublier de remercier tous ceux qui, de près ou de loin, ont participé pour la réalisation de ce travail.

#### **Abstract**

As CMOS technology scaling continues, subthreshold leakage current increases dramatically. A significant percentage of the total chip power is due to leakage sources, also known as static power. Accurately estimating static power in early stages of design is an important step for developing power efficient products. Leakage current is an important segment of total supply current, which is used as a means to identify defective chips. Leakage current value is determined by the sum of leakage currents of those transistors that can leak. Setting leakage current value too high or low will result in excessive shipment of defective chips or yield loss because of rejecting good parts, respectively. So it is important to analyse leakage current in circuits in order to reduce theme. Reducing power dissipation is a design goal in devices since excessive power dissipation results in increased packaging and cooling costs as well as potential reliability problems. Our purpose in this work consists in highlighting certain leakage currents by SPICE and MATLAB simulation in submicron structures MOSFET such as the short channel transistor: the BSIM4.we did focus mainly in this study on sub- threshold, I<sub>GIDL</sub>, I<sub>DIBL</sub>, I<sub>DIF</sub>, Ion currents.

Key words: MOSFET, GIDL, DIBL, IOFF, ION, Leakage Current, Sub threshold current, Electrical simulation.

#### Résumé

Le courant de fuite sous seuil augmente considérablement avec des technologies de plus en plus évolué. Un pourcentage considérable de la puissance totale des puces conçues est dû aux courants de fuite, également connue sous le nom de puissance statique. Estimer exactement la puissance statique aux premières étapes de toute conception est une étape importante pour développer des produits à rendement en puissance efficace. Le courant de fuite est une partie importante du courant total. Ce courant de fuite est employé comme référence pour la détermination des puces défectueuses. Il est déterminé par la somme des courants de fuite du composent et plus exactement des transistors élémentaires la constituant.

Une valeur de courant de fuite choisi adéquatement retenue en référence, permettra d'éliminer les puces défectueuse et d'éviter de se débarrasser de celles non défectueuses. La dissipation excessive de puissance a pour conséquence des coûts d'encapsulation et de refroidissement accrus aussi bien que des problèmes de fiabilité.

Le but de ce travail est de mettre en évidence certains courants de fuite dans des transistors à canaux courts tel que BSIM4 employant les logiciels de simulation électrique SPICE et MATLAB. Nous nous sommes intéressé principalement dans cette étude aux courants : sous seuil, I<sub>GIDL</sub>, I<sub>DIBL</sub>, I<sub>OFF</sub>, Ion.

Mots Clé: MOSFET, DIBL, GIDL, ION, IOFF, Courant De Fuite, Courant Sous Seuil, Simulation électrique.

#### ملخص

إن تيار التسرب دون عتبة يزيد بشكل كبير مع تقدم التكنولوجيا الحالية . و نسبة كبيرة من طاقة الرقاقات المصممة الإجمالية سببها تيارات التسرب ، المعروفة أيضا باسم الطاقة الثابتة إن التقدير الدقيق للطاقة الثابتة في المراحل الأولى من أي تصميم هو خطوة هامة في تطوير منتجات ذات مردود طاقوي فعال تيار التسرب جزء مهم من التيار الكلى. هذا التيار

#### Dédicace

المتسرب يستخدم كمرجع لتحديد الرقائق الغير صالحة. ويمكن تعريفه بمجموع تيارات التسرب وبالأحرى في التر انز ستورات التي تعتبر المكونات الجزئية للرقاقة.

ان قيمة مناسبة لتيار التسرب مختارة كمرجع ،تسمح بالقضاء على الرقاقات الفاسدة والحفاظ على تلك الجيدة كما أن تبديد الطاقة المفرط ينتج تكاليف مبهضة للتغليف و التبريد فضلا عن مشاكل المردود.

والهدف من هذا العمل هو تسليط الضوء على البعض من تيارات التسرب في الترانزستورات ذات قناة قصيرة مثل السلامية الله MISB4

باستخدام برنامجي المحاكاة الكهربائية SPICE و MATLAB.

$I_{\rm ON}$  ,  $I_{

m OFF}$  ,  $I_{

m GIDL}$  ,  $I_{

m DIBL}$  ، تحت عتبة عتبة وقد اولينا الاهتمام بشكل رئيسي في هده الدر اسة لتيار ات

كلمات المفتاح: MOSFET, DIBL, GIDL, ION, IOFF, تيار التسرب تيار تحت العتبة, المحاكاة الكهربائية.

# Table des matières

| LISTE DES FIGURES ET TABLEAUX                                                                       | 7  |

|-----------------------------------------------------------------------------------------------------|----|

| TABLE DES SYMBOLES                                                                                  | 10 |

| INTRODUCTION GENERALE                                                                               | 13 |

| CHAPITRE - I                                                                                        | 17 |

| Etude Theorique Des Transitors MOSFET                                                               |    |

| I. Historique                                                                                       | 18 |

| II. Constitution                                                                                    | 18 |

| II.1. Réalisation physique                                                                          | 18 |

| II.2. Différents types de structures de base                                                        | 20 |

| III.3. Symboles des différentes structures de base                                                  | 21 |

| III.Principe de fonctionnement                                                                      | 23 |

| III.1. Sans polarisation de grille par rapport au substrat                                          | 23 |

| III.2. La grille est polarisée positivement par rapport au substrat                                 | 24 |

| III.3. La polarisation de la grille atteint la tension de seuil : $V_{GS} > V_{th}$                 | 25 |

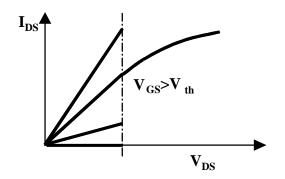

| III.4. Caractéristique $I_{DS}(V_{DS})$ d'un transistor NMOS à enrichissement de canal :            | 26 |

| III.4.1. La tension drain-source $V_{DS}$ est faible                                                | 26 |

| III.4.2. La tension de grille $V_{GS} > V_{th}$ et la tension drain-source $V_{DS}$ non négligeable | 27 |

| III.5. Caractéristique de sortie du transistor $I_{DS}$ ( $V_{DS}$ , $V_{GS}$ )                     | 29 |

| IV. Analyse physique de la structure métal/oxyde/semi-conducteur idéale                             | 29 |

| IV.1. Diagramme d'énergie à l'équilibre thermodynamique                                             | 29 |

| IV.2. Régime d'accumulation                                                                         | 31 |

| IV.3. Régime de désertion                                                                           | 33 |

| IV.4. Régime de faible inversion                                                                    | 33 |

| IV.5. Régime de forte inversion                                                                     | 34 |

| IV.6. Capacité équivalente de la structure MOS :                                                    | 35 |

| V. Caractéristique d'un transistor MOS idéal                                                        | 37 |

| V.1. Expression de la charge dans le canal                                                          | 37 |

| V.2. Calcule du courant                                                                             | 39 |

| VI. Modèle petit signal du MOSFET en saturation sans effet de substrat du MOS                       | 42 |

| VI.1. Capacités du MOS                                                                              | 43 |

| VI.2. Modèles du MOS Utilisés en simulation                                                         | 44 |

| VI.2.1. Régime d'inversion du transistor MOS                                                         | 44 |

|------------------------------------------------------------------------------------------------------|----|

| VII. Effet des canaux courts dans les transistors MOSFET                                             | 45 |

| VII.1. Définition                                                                                    | 45 |

| VII.2. Impact sur la tension de seuil                                                                | 45 |

| VII.3. Effets d'ionisation par impact                                                                | 48 |

| VII.4. Effets thermiques                                                                             | 50 |

| VII.5. Les avantages des transistors MOS :                                                           | 51 |

| VIII. Conclusion                                                                                     | 52 |

| CHAPITRE - II                                                                                        | 53 |

| Etude Des Courants De Fuites Dans Les Transistors MOSFET                                             |    |

| I. Etude du model BSIM4                                                                              | 54 |

| I.1. Introduction                                                                                    | 54 |

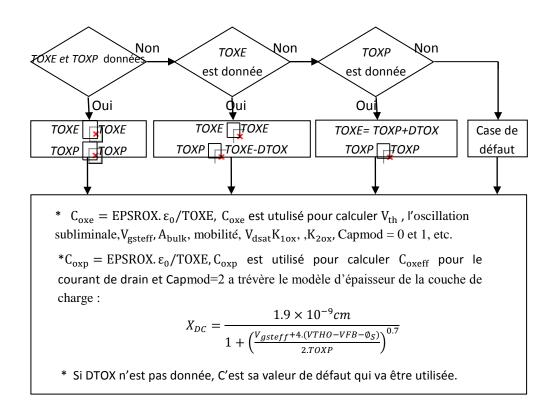

| I.2. Model de diélectrique de grille                                                                 | 56 |

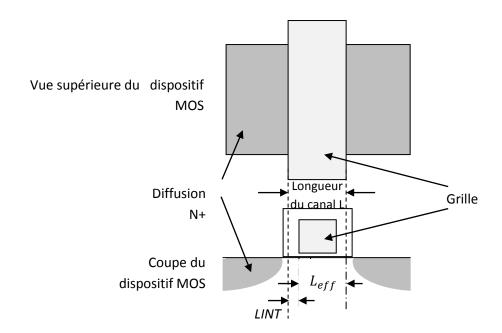

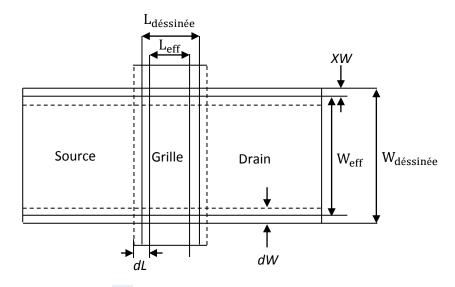

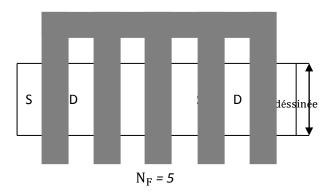

| I.3. Modèles de longueur et largeur effectives du canal                                              | 57 |

| I.4. Potentiel de surface et profondeur de déplétion :                                               | 59 |

| II. Les courants de fuites dans les MOSFETS                                                          | 61 |

| II.1. Introduction                                                                                   | 61 |

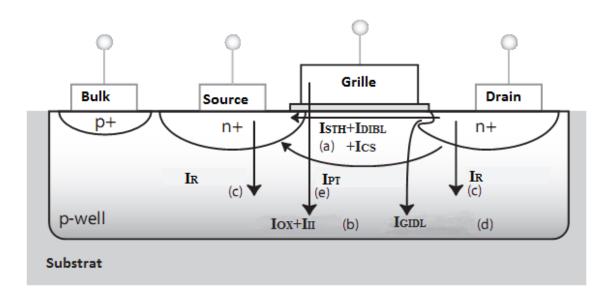

| II.2. Courants de fuite du MOSFET                                                                    | 62 |

| II.3. Courants sous seuil                                                                            | 64 |

| II.3.1. Effet de faible inversion                                                                    | 64 |

| II.3.2. Abaissement de la barrière de potentiel par le drain (DIBL : Drain Induced Barrier Lowering) | 64 |

| II.4. Effet De substrat                                                                              | 68 |

| II.5. Effet de longueur du canal                                                                     | 68 |

| II.6. Courant de fuite du drain induit par la grille (GIDL)                                          | 68 |

| II.7. Courant de polarisation inverse de la jonction p-n                                             | 69 |

| II.8. Courant de conduction sous le seuil                                                            | 69 |

| II.9. Le courant tunnel à travers l'oxyde de grille I <sub>OX</sub>                                  | 70 |

| II.10. Le courant de grille dû à l'injection de porteurs chauds                                      | 71 |

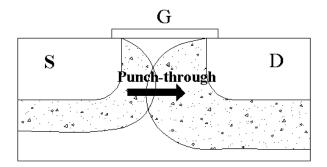

| II.11. Courant de perforation (Channel punch-through leakage)                                        | 71 |

| III. Paramètres des quels dépendent les courants de fuite                                            | 71 |

| IV. Conclusion                                                                                       | 72 |

| CHAPITRE - III                                                               | 73 |

|------------------------------------------------------------------------------|----|

| Présentation Des Résultats Et Interprétation                                 |    |

| I. Introduction                                                              | 74 |

| II. Caractéristiques I-V du model BSIM4                                      | 76 |

| II.1. Simulation des courants de fuite d'une structure MOSFET                | 77 |

| II.2. Analyse des effets des canaux courts sur la tension de seuil du MOSFET | 90 |

| III. Conclusion                                                              | 92 |

| CONCLUSION GENERALE                                                          | 93 |

| REFERENCES BIBLIOGRAPHIQUES                                                  | 96 |

| ANNEXES                                                                      | 99 |

# Liste Des Figures

## Chapitre -I- : Etude théorique des transistors MOSFET

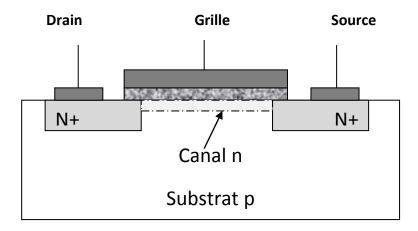

| Figure I.1:    | Coupe schématique d'un transistor MOS à canal n. Au repos                                        | 19 |

|----------------|--------------------------------------------------------------------------------------------------|----|

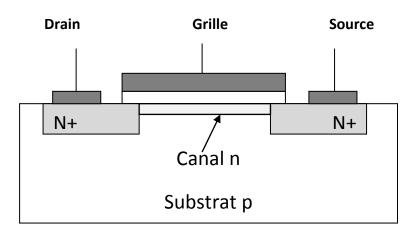

| Figure I.2 :   | Coupe schématique d'un transistor NMOS normalement conducteur                                    | 20 |

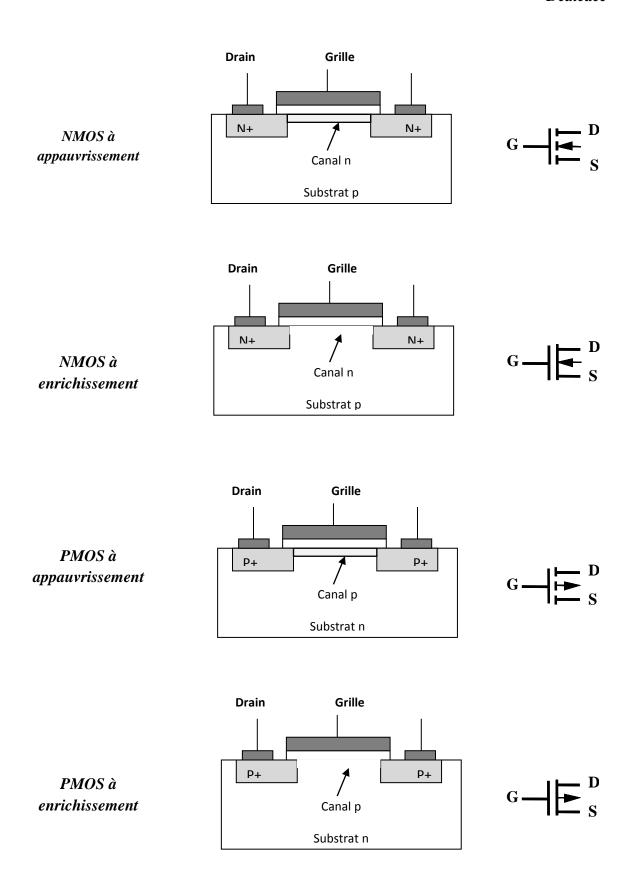

| Figure I.3 :   | Coupes et représentations symboliques des différents types de transistors MOS2                   | 22 |

| Figure I.4 : ' | Transistor NMOS à l'équilibre thermodynamique                                                    | 23 |

| Figure I.5 :   | Création de la zone de charge d'espace sous la grille                                            | 24 |

| Figure I.6 : ( | Création du canal lorsque la tension de grille devient supérieure ou égale à la tension de seuil |    |

| Figure I.7 :   | La variation de la résistance interne du transistor vue entre le drain et la source?             | 26 |

| Figure I.8 : I | Modification de la forme du canal d'électron                                                     | 27 |

| Figure I.9 :   | Evolution de la caractéristique $I_{DS}(V_{GS})$ $I_{DS}(V_{GS})$                                | 27 |

| Figure I.10 :  | Déplacement du point de pincement                                                                | 28 |

| Figure I.11 :  | Caractéristique de sortie du transistor MOS2                                                     | 29 |

| Figure I.12 :  | Diagrammes d'énergie à l'équilibre thermodynamique des différents matériaux de la structure MOS  | 30 |

| Figure I.13    | : variation du potentiel à travers la structure                                                  | 31 |

| Figure I.14 :  | Diagramme de bandes d'énergies pour un MOSFET à Canal n à désertion                              | 32 |

| Figure 1.15 :  | Représentation de la distribution des charges dans la structure en régime de for inversion       |    |

| Figure I.16 :  | Variation de la capacité normalisée en fonction de la tension de grille                          | 36 |

| Figure I.17 :  | Représentation schématique de la structure MOS en régime de conduction non saturée               | 38 |

| Figure I.18 :  | Caractéristique de transfert typique d'un transistor NMOS intégré                                | 41 |

| Figure I.19 :  | Réseau de Caractéristiques I (V) d'un MOSFET idéal                                               | 41 |

| Figure I.20    | Schéma équivalent du MOS en régime petits signaux sans effet de substrat                         | 42 |

| Figure I.21 :  | Capacités de terminaison du MOS                                                                  | 43 |

| Figure I.22 :  | Distribution de la charge de désertion contrôlée par la grille                                   | 45 |

| Figure I.23 :  | Caractéristiques $I_D/V_D$ d'un transistor MOS à canal court                                     | 46 |

| _              | : Caractéristiques $I_D/V_G$ du transistor MOS en régime sous seuil $P$ our $I_D$                | 47 |

| Figure I.25 : Evolution de la tension de seuil en fonction de la longueur du canal                                   | -48        |

|----------------------------------------------------------------------------------------------------------------------|------------|

| Figure I.26: schématisation du phénomène d'ionisation par impact dans un transistor à cana                           |            |

| Chapitre -II- : Etude des courants de fuites dans les transistors MOSFET                                             | •          |

| Figure II.1 :Nombre de paramètres DC du modèle en fonction de l'année de l'introduction du modèle                    |            |

| Figure II.2 : Caractéristique $I_{DS}$ en fonction de $V_{DS}$ du modèle $BSIM4$                                     | -55        |

| Figure II.3: Illustration des options pour les modèles du diélectrique de grille du BSIM4                            | -57        |

| Figure II.4: Représentation de la longueur effective du canal                                                        | 58         |

| Figure II.5: Définition de XL, XW, dW, Weff et Leff                                                                  | 58         |

| Figure II.6: définition deW <sub>dessinée</sub> , et NF                                                              |            |

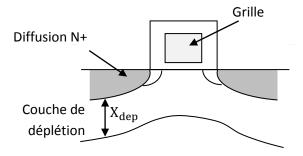

| Figure II.7: Illustration de la profondeur de déplétion Xdep                                                         | -61        |

| Figure II.8: Illustration des différents courants de fuite présents dans un transistor fortement sous-micronique.    |            |

| Figure II.9: Profile du potentiel de surface pour des transistors n-MOS                                              | -65        |

| Figure II.10: Evolution du potentiel de surface pour des dispositifs de différentes longueurs canal.                 |            |

| Figure II.11: Courbes de transfert pour des tensions de drain de 0.1V(Régime linéaire) et 1.5 (régime de saturation) |            |

| Figure II.12: Caractéristique $I_D(V_{GS})$ d'un transistor NMOS montrant le GIDL dans la technologie $0,13\mu m$ .  | <i>6</i> 8 |

| Figure II.13 : Influence de la tension de seuil sur les courants de fuite d'un transistor NMOS -                     | -69        |

| Figure II.14: Extension des zone de déplétion dans le substrat conduisant au phénomène de punch-through              |            |

| Chapitre -III- : Présentation des résultats et interprétation                                                        |            |

| Figure III.1 : Caractéristiques théorique $I_{DS}$ - $V_{GS}$ à $V_{BS}$ =0 du BSIM4                                 | ·- 75      |

| Figure III.2 : Schéma équivalent DC implémenté par le BSIM4                                                          | - 75       |

| Figure III.3 : Schéma du circuit permettant la mise en évidence des courants de fuite du MOSFET                      | <i>77</i>  |

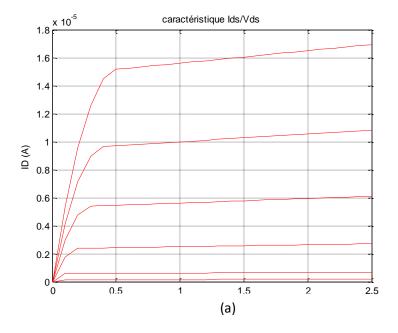

| Figure III.4 : Caractéristique $I_{DS}$ en fonction de $V_{DS}$ à $V_{GS}$ constant et $V_{BS}$ =0 $V$               | 78         |

| Figure III.5 : Mise en évidence de la zone d'ionisation par impact                                                   | - 79       |

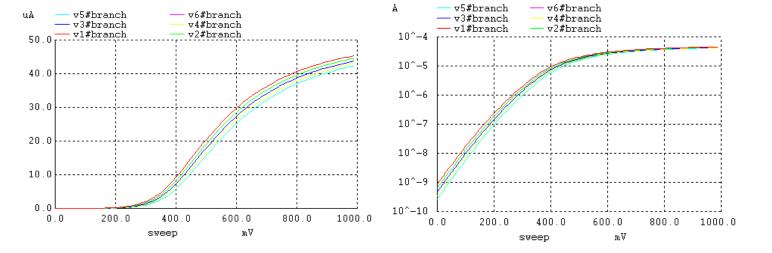

| Figure III.6 : Caractéristique de transfert $I_{DS}$ - $V_{GS}$ ,(a) échelle linéaire, (b) échelle logarithmique                                                                                                                               | - <i>7</i> 9 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

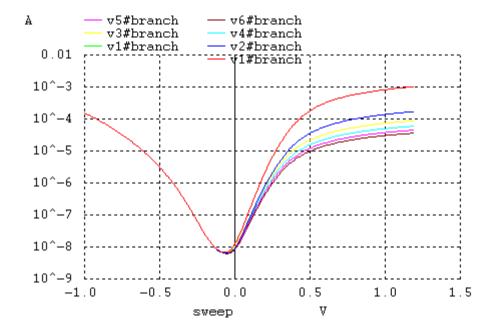

| Figure III.7.A: Caractéristiques I <sub>DS</sub> -V <sub>GS</sub> à V <sub>BS</sub> variable du BSIM4 en technologie 50nm (Environnement MATLAB)                                                                                               | -80          |

| Figure III.7.B : Caractéristiques I <sub>DS</sub> -V <sub>GS</sub> à V <sub>BS</sub> variable du BSIM4 en technologie 50nm (Environnement SPICE)                                                                                               | -81          |

| Figure III.8: Caractéristiques I <sub>DS</sub> -V <sub>GS</sub> à V <sub>BS</sub> variable du BSIM4 en technologie 50nm (W/L=0.5/0.05, V <sub>DS</sub> =1V),(a) échelle linéaire, (b) échelle logarithmique                                    | -82          |

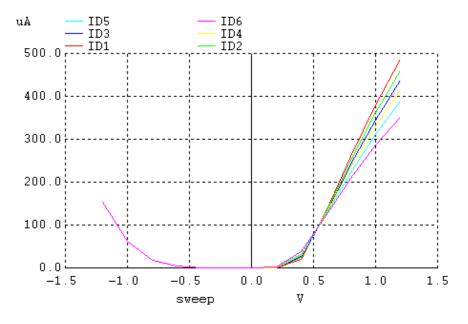

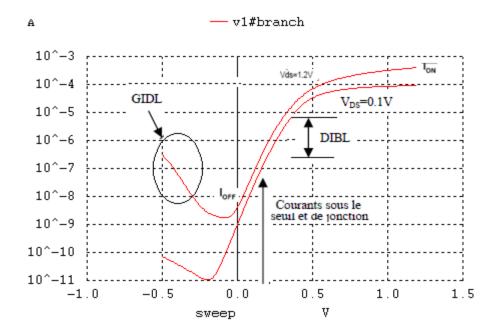

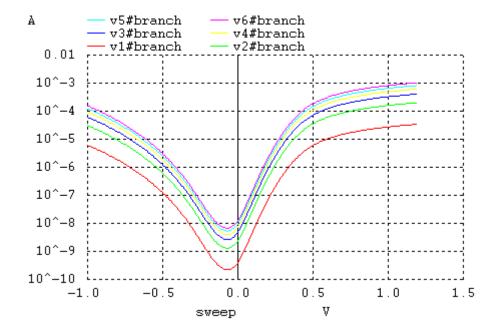

| Figure III.9: Mise en évidence des courants de fuite $I_{OFF}$ , $I_{GIDL}$ du BSIM4 en technologie 50nm (W/L=0.5/0.05, (a): $V_{DS}$ =1.2V, (b): $V_{DS}$ =0.5V,(c) technologie 65nm)                                                         |              |

| Figure III.10 : Influence de la température sur le courant de fuite I <sub>OFF.</sub>                                                                                                                                                          | -85          |

| Figure III.11: Invariance du courant I <sub>GIDL</sub> avec la température.                                                                                                                                                                    | -86          |

| Figure III.12: Caractéristique log I <sub>DS</sub> (V <sub>GS</sub> ) d'un transistor NMOS montrant les composantes principales du courant I <sub>OFF</sub>                                                                                    |              |

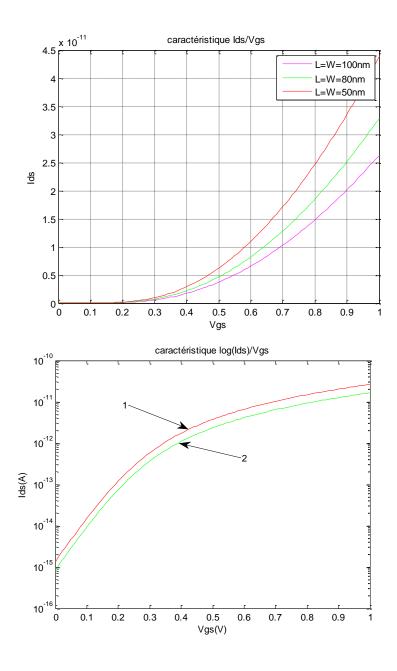

| Figure III.13: Caractéristique log I <sub>DS</sub> (V <sub>GS</sub> ) d'un transistor NMOS montrant les composantes principales du courant I <sub>OFF</sub> la technologie CMOS 50nm Pour une longueur variable et une largeur constante =50n. | 00           |

|                                                                                                                                                                                                                                                | .00          |

| Figure III.14: Caractéristique log I <sub>DS</sub> (V <sub>GS</sub> ) d'un transistor NMOS montrant les composantes principales du courant I <sub>OFF</sub> la technologie CMOS 50nm Pour une longueur constante=50n et une largeur variable   | -89          |

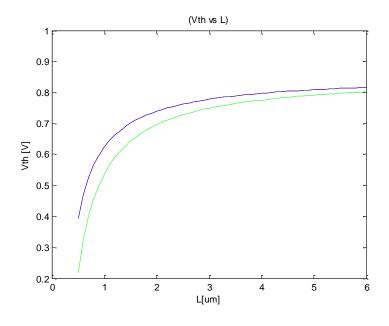

| Figure III.15: impact des effets des canaux courts sur la tension de seuil du transistor                                                                                                                                                       |              |

| Figure III.16: variation de la tension de seuil en fonction de la longueur du canal                                                                                                                                                            |              |

| Liste Des Tableaux                                                                                                                                                                                                                             |              |

| Tableau I.1 : les valeurs de capacités de terminaison en fonction des capacités intrinsèques p chaque zone de fonctionnement du MOS                                                                                                            |              |

| Tableau II 1 · Paramètres influencent les courants de fuite                                                                                                                                                                                    |              |

BSIM: Berkeley Short-Channel IGFET Model.

BC: Bande de conduction.

BV: Bande de valence.

CMOS: Complementary Metal Oxyde Semiconductor.

*CLM* : Channel-length modulation.

$C_{ox}$ : La capacité de l'isolant (Oxyde) par unité de surface.

$C_{ZCE}$ : La capacité surfacique.

$C_{ab}$ : Capacité grille-Substrat.

$C_{ad}$ : Capacité grille-drain.

$C_{qs}$ : Capacité grille-source.

$C_{db}$ : Capacité grille-Substrat.

$C_{sb}$ : Capacité grille-drain.

C<sub>j</sub> : La capacité zone de déplétion.

$C_{oxeff}$ : La capacité effective d'oxyde de grille.

DIBL: Drain Induced Barrier Lowering.

DITS: Drain-induced thershold shift.

DTOX : La différence l'épaisseur électrique de grille et l'épaisseur physique.

$E_C$ : Energie du niveau le plus bas de la bande de conduction.

$E_V$ : Energie du niveau le plus haut de la bande de conduction.

$E_F$ : Niveau de fermi du semi-conducteur.

$E_{F_m}$ : Niveau de fermi du métal.

$E_i$ : La position du niveau de fermi du semi-conducteur intrinsèque.

$E_{ox}$ : Le champ à l'interface isolant semi-conducteur.

$E_{eff}$ : Le champ effectif.

g: La conductance du canal.

K: La constante de Boltzmann. ( $K=1.38x10^{23}$  J.K-1)

L: La Longueur de canal dessiné.

$L_{eff}$ : La longueur effective du canal.

$l_t$ : La longueur caractéristique.

MOS: Métal Oxyde Semi-conducteur.

MOSFET: (Metal Oxyde Semiconductor Field Effect Transistor).

*NSD*: la concentration des dopants source/drain.

*NULD* : non-uniforme latéral doping.

$N_a$ : La concentration des atomes accepteurs.

$N_d$ : La concentration des atomes donneurs.

NV: Niveau de vide.

n : La densité des électrons.

$n_i$ : La concentration intrinsèque des porteurs.

NMOS: transistor MOS à canal N.

PMOS: transistor MOS à canal P.

p : La densité des trous.

q: La valeur absolu de la charge de l'électron ( $q = 1.602x10^{-19}$  Cb)

$Q_s$ : La densité d'électron par unité de surface dans le semi-conducteur.

Q<sub>m</sub>: La densité de trous par unité de surface dans le métal.

$Q_n$ : La charge dans la zone d'inversion.

$Q_{SS}$ : La charge piégée dans ces états d'interfaces.

$Q_{dep}$ : La charge de déplétion.

$Q_B$ : La densité de charge en bulk.

RSCE: Reverse short-channel effect.

$R_G$ : Résistance de la grille du MOSFET

$R_B$ : Résistance du substrat.

$R_{SD}$ : Résistance série ( $R_{SD} = R_S + R_D$ ).

SCE: Short Channel Effect.

*SCBE*: Substrate current-induced body effect.

TMOS: Transistor MOS.

TOXE : Epaisseur électrique d'oxyde de grille.

*TOXP* : Epaisseur physique de l'oxyde de grille.

*T* : La température absolue.

$T_{ox}$ : Epaisseur de l'oxyde.

$V_{FB}$ : La tension de bandes plates (flat band).

$V_T$ : La tension seuil.

$V_{ox}$ : La différence de potentiel de part et d'autre de l'oxyde.

$V_{dsat}$ : La tension de saturation du transistor MOSFET.

$V_d$ : La tension du drain.

$V_{DD}$ : Tension d'alimentation nominale.

$V_G$ : Tension appliqué sur la grille.

$V_{DS}$ : Tension Drain – Source.

$V_{bi}$ : La barrière de potentiel de la jonction source/drain.

$W_{total}$ : La largeur totale du transistor.

$W_{eff}$ : La largeur effective du canal.

$X_{dep}$ : Profondeur de déplétion.

XJ: La profondeur de la jonction source-drain.

$\chi$ : Affinité électronique du semi-conducteur.

ZTC: Zero Temperature Coefficient.

ZCE : zone de charge d'espaces.

$\emptyset_S$ : Travail de sortie du semi-conducteur.

$\emptyset_m$ : Travail de sortie du métal.

$\emptyset_{ms}$ : Différence des travaux de sortie du métal et du semi-conducteur.

$\varepsilon_{ox}$ : La constante diélectrique d'oxyde.

$\varepsilon_0$ : Permittivité du vide (= 8.85x10<sup>-12</sup> F.m<sup>-1</sup>).

$\varepsilon_i$ : Constante diélectrique de l'isolant.

$\Psi_{S}$ : Le potentiel de surface.

$\sigma$ : La conductivité du canal.

ρ: Densité de charges.

$\Delta E_d$ : L'énergie d'ionisation du niveau donneur.

$\mu_{eff}$ : Mobilité effective des électrons dans le canal.

$\gamma$  : Le coefficient de polarisation du substrat.

# **INTRODUCTION GENERALE**

#### Introduction générale

L'augmentation de la densité d'intégration et la rapidité des circuits croit sans cesse, ce fait a conduit au développement des dispositifs submicroniques. Chaque année, les chercheurs s'emploient à réduire la taille de ces dispositifs. L'épaisseur d'oxyde de grille minimum actuellement atteinte est de 20A° soit 7 couches atomiques. Toutefois, on ne peut réduire les dimensions sans prendre en compte certains effets particuliers propres aux dispositifs de petites tailles.

Dans ce travail, nous présentons, le transistor MOS (Métal Oxyde Semi-conducteur) sur silicium utilisés en architecture CMOS (Complementary MOS: MOS Complémentaires) qui est l'un des principaux artisans de cette progression continuelle et domine de façon écrasante le marché des semi-conducteurs. Depuis l'apparition du transistor MOSFET, des améliorations incessantes ont permis de l'intégrer au quotidien dans des applications de plus en plus complexes dans l'industrie. Plusieurs model se sont succédés avec la miniaturisation et la forte densité d'intégration respectant la loi de MOORE, on citera entre autre les modèles MM9, MM11, EKV et la famille BSIM tous considérés comme des transistors à canaux courts.

L'un des facteurs à prendre en compte lors de la conception des transistors est les courants de fuite dissipant de l'énergie inutilement et altérant le fonctionnement des transistors MOSFET à canaux courts, altérant par la même occasion le

fonctionnement des circuits. De ce fait, il devient alors indispensable, de considérer ces courants de fuites et les paramètres ayant une influence directe sur ces courants et pouvant les amplifier. Ce courant sous seuil de fuite augmente considérablement avec des technologies de plus en plus basses. Un pourcentage considérable de la puissance totale des puces conçues est dû aux courants de fuite, également connue sous le nom de puissance statique. Estimer exactement la puissance statique aux premières étapes de toute conception est une étape importante pour développer des produits à rendement en puissance efficace. Le courant de fuite est une partie importante du courant total de la puce (IDSQ). Ce courant de fuite est employé come référence pour la détermination des puces défectueuses. Il est déterminé par la somme de courants de fuite de la puce et plus exactement des transistors la valeur constituant. Une de courant de fuite choisi adéquatement retenue en référence, permettra d'éliminer les puces défectueuse et d'éviter de se débarrasser des puces non défectueuses.

On se propose dans cette étude d'étudier généralement les courants de fuite des structures MOSFET à canaux courts et de les identifier dans un model de transistor à canaux court : le BSIM4, en employant le logiciel SPICE. Le centre principal de cette étude sera les mécanismes de courant sous seuil, GIDL, DIBL,  $I_{FF}$ ,  $I_{ON}$

Notre travail est scindé en trois chapitres:

Le premier chapitre est destiné à l'étude théorique des transistors MOS où on rappelle les notions et les équations de bases pour les différentes structures et leurs fonctionnements. La première partie est dédiée à la description de la structure MOS idéal et sont fonctionnement ainsi que les étapes de calculs de ses caractéristiques électriques, puis la structure MOS réelle et son fonctionnement en mode statique et en mode dynamique

Le deuxième chapitre est consacré à une étude théorique du modèle BSIM4, où on va présenter les principaux paramètres et équations qui le caractérisent, pour une simulation sur ordinateur, ainsi que les effets physiques pris en compte dans ce modèle. On présentera dans la deuxième partie de ce chapitre les différents courants de fuite, dissipant inutilement de la puissance dans les MOSFET altérant ainsi leur fonctionnement.

Le troisième chapitre sera consacré à la mise en évidence par simulation de certains courants de fuite dans le BSIM4 avec présentation des paramètres influençant ces courants de fuite.

Une conclusion générale permettra de faire la synthèse des résultats obtenus.

# CHAPITRE - I ETUDE THEORIQUE DES TRANSITORS MOS

#### I. Historique

Le transistor MOSFET est apparut réellement au début des années 1960 bien que son principe ait été proposé dès le début du 20ème siècle. C'est la maîtrise technologique des procédés appliqués au silicium à la place du germanium et plus particulièrement la mise en œuvre des oxydes minces de silicium qui a permis le développement fabuleux de la technologie CMOS.

#### **II. Constitution**

#### II.1. Réalisation physique

La structure Métal/Isolant/Semi-conducteur ou Métal/Oxyde/Semi-conducteur, que l'on nomme plus communément MOS, est basée sur la commande par une polarisation sur une électrode isolée de porteurs libres dans une zone peu dopée. La modulation du nombre de porteurs permet d'établir un canal de conduction entre deux zones conductrices correspondant à des zones semi-conductrices très dopées.

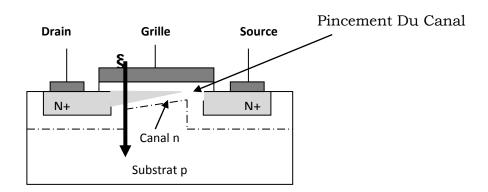

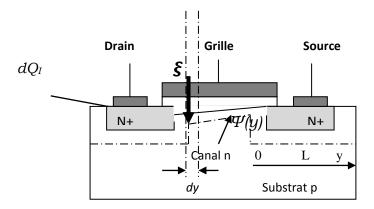

La Figure I.1 présente une coupe schématique de la structure MOS. L'électrode de commande s'appelle grille, les deux autres, source et drain. Cette terminologie sera justifiée dans la suite. La grille est constituée d'une couche isolante de très faible épaisseur, en général de l'oxyde de silicium, SiO2, surmontée d'une couche très conductrice telle qu'un métal ou dans le cas des circuits intégrés du silicium très dopé. Les zones de semi-conducteur de source et drain sont recouvertes d'une couche métallique permettant d'établir un bon contact électrique avec les circuits extérieurs.

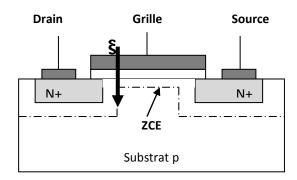

**Figure I.1 :** Coupe schématique d'un transistor MOS à canal n. Au repos

Pour que sans polarisation de grille le courant circulant entre les deux électrodes source et drain soit négligeable, la zone de canal à l'équilibre thermodynamique doit être de type opposé aux zones de source et drain afin d'avoir, quel que soit le sens de la polarisation entre ces deux zones, une jonction polarisée en inverse et qui est donc bloquante ; la structure est équivalente à deux diodes tête-bêche. Ainsi, si la source et le drain sont de type n comme représentées Figure I.1, alors la zone sous la grille isolée est de type p.

Par l'action d'une polarisation sur le contact de grille par rapport à la zone semi-conducteur, il se crée un champ électrique qui va agir sur la zone semi-conductrice sous l'oxyde (c.a.d par rapport au Bulk). Pour assurer une conduction, il faut dans l'exemple de la Figure I.1 que des électrons viennent prendre la place des trous. Il se crée dans ces conditions un canal induit de type n. L'application d'une polarisation positive sur la grille conduira à cet effet. Le transistor est nommé dans ces conditions MOS de type n ou plus simplement NMOS.

Puisque au repos le transistor de la Figure I.1 ne conduit pas, nous dirons qu'il est de type à enrichissement, *normally off* en anglais.

<u>NB</u>: un raisonnement similaire se fait pour des transistors PMOS. Dans ce cas le substrat, la source et le drain seront de type N, et le canal induit sera de type P.

#### II.2. Différents types de structures de base

Telle que nous l'avons décrite ci-dessus, la structure ne conduit pas entre la source et le drain au repos, c'est-à-dire lorsque aucune tension n'est appliquée sur la grille ; en pratique, il est possible de réaliser une couche très fine et suffisamment dopée juste sous l'isolant de même type que les zones de sources et de drain afin de permettre une conduction au repos : trois zones dopées du même type sont en série. Par contre, l'application d'un champ électrique peut « chasser » les électrons de ce canal existant au repos et donc peut entraîner le blocage de la conduction. La Figure I.2 montre la coupe schématique d'une telle structure. Ce transistor est alors appelé transistor NMOS à appauvrissement dit normally on, en anglais.

**Figure I.2 :** Coupe schématique d'un transistor NMOS normalement conducteur (à appauvrissement)

Les Figures I.1et I.2 sont données pour des transistors à canal n. Nous pouvons remplacer par analogie le dopage de type n des zones de sources et de drain par un dopage de type p, et le dopage du substrat de type p par du

type n et éventuellement celui du canal en surface par du type p. Nous créons dans ce cas des transistors PMOS soit à enrichissement, soit à appauvrissement. Il existe donc 4 types de transistors MOS.

- Le NMOS à enrichissement de canal

- Le NMOS à appauvrissement de canal

- Le PMOS à enrichissement de canal

- Le PMOS à appauvrissement de canal

#### II.3. Symboles des différentes structures de base

Les quatre types possibles de transistors sont représentés ci-dessous avec leurs symboles conventionnels. Il faut noter que pour des simplicités graphiques certains catalogues et ouvrages utilisent des formes légèrement différentes. La Figure I.3 recense ces structures.

De façon symbolique, une flèche apparaît entre le substrat et le canal. Cette flèche est orientée dans le sens passant de la jonction pn fictive substratcanal. Par exemple, dans le cas du NMOS à enrichissement, la flèche est orientée dans le sens substrat-canal.

**Figure I.3 :** Coupes et représentations symboliques des différents types de transistors MOS.

#### III. Principe de fonctionnement

Le principe de fonctionnement des transistors à grille isolée est effectue en prenant comme exemple un transistor NMOS à enrichissement de canal, et en considérant les couches idéales. Nous verrons plus loin en détail ce que cela signifie.

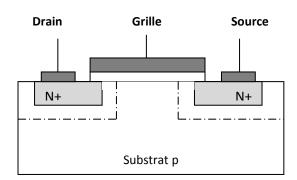

#### III.1. Sans polarisation de grille par rapport au substrat

Le circuit électrique entre la source et le drain est toujours constitué de deux diodes à jonction pn montées en tête-bêche. Quel que soit le signe d'une polarisation drain-source, automatiquement, l'une des deux diodes est polarisée en inverse ce qui signifie que le courant dit drain-source,  $I_{DS}$  peut être considéré nul ou tout au moins négligeable.

A l'équilibre thermodynamique, il existe en permanence une zone de charge d'espace entre le drain et la zone de substrat, ainsi qu'entre la source et le substrat (Figure I.4). Il faudra être attentif aux extensions de ces zones qui doivent bien sûr être inférieures à la distance entre les jonctions métallurgiques pour éviter de mettre en court- circuit les zones de source et de drain.

**Figure I.4 :** Transistor NMOS à l'équilibre thermodynamique.

<u>NB</u>: au niveau du substrat, la structure source-substrat-drain (*npn*) a l'aspect d'un transistor bipolaire. Puisqu'il n'y a aucune polarisation directe des jonctions source-substrat ou drain- substrat, le substrat qui pourrait jouer le rôle de la base n'est pas alimenté et ne provoque donc aucune injection ; il n'y a donc pas d'effet transistor bipolaire, dans ces conditions.

#### III.2. La grille est polarisée positivement par rapport au substrat

Le circuit électrique entre la source et le drain est toujours constitué de deux diodes à jonction. L'application d'un potentiel  $V_G>0$  sur la grille, entraîne la création d'un champ électrique orienté vers le substrat à la fois dans l'oxyde et dans le semi-conducteur. En général, la référence est le substrat et quand ce dernier est court-circuiter à la source, la référence sera donc la source, si bien que nous noterons dans la suite  $V_{GS}>0$ .

Ce champ dans le semi-conducteur a tendance à chasser les trous près de l'interface et donc à déserter la zone sous la grille ceci est représenter en Figure I.5, puisque les ions accepteurs sont immobiles. Il se crée ainsi une zone de charge d'espace (ZCE) sous la grille qui prolonge les deux zones latérales préexistantes. Pour un champ électrique faible, la zone de charge d'espace correspond essentiellement à l'évacuation de trous qui sont majoritaires dans cette zone dopée de type p.

**Figure I.5 :** création de la zone de charge d'espace sous la grille par la présence d'un champ électrique.

Si le champ dans le semi-conducteur augmente intuitivement, celui-ci peut devenir suffisant pour attirer les porteurs minoritaires qui viennent s'agglutiner sous l'oxyde. Il se forme alors progressivement un canal d'électrons contre l'oxyde. La transition entre la source et le drain devient possible et un faible courant  $I_{DS}$  peut commencer à circuler dans le canal.

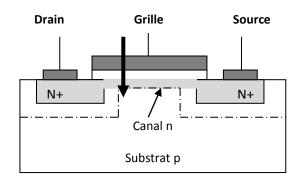

#### III.3. La polarisation de la grille atteint la tension de seuil : V<sub>GS</sub>>V<sub>TH</sub>

En augmentant  $V_{GS}$ , on augmente le champ électrique dans le substrat près de l'interface oxyde substrat et la concentration en électrons continue à augmenter. A l'interface oxyde-substrat, coté semi-conducteur, la concentration en électrons peut atteindre la valeur du dopage, c'est-à-dire la concentration en trous initiale du substrat : partie foncée du canal entre les deux zones dopées N+ sur la Figure I.6.

**Figure I.6**: Création du canal lorsque la tension de grille devient supérieure ou égale à la tension de seuil.

Dans ces conditions, nous dirons qu'il y a une inversion de population de porteurs et que la tension de grille a atteint la tension de seuil du transistor ( $V_{TH}$ ). Nous dirons aussi que le canal est créé.

La conduction entre source et le drain peut devenir importante et le transistor sera dit en *régime de conduction*. Ainsi, par application d'une tension positive sur la grille, il est possible de commander un courant entre la source et le drain.

En régime continu ou aux basses fréquences, le courant traversant la grille peut être considérer nul .Le dispositif est donc un *convertisseur tension-courant* (entrée-sortie) qui sera d'autant meilleur qu'une faible tension pilote un fort courant (transconductance élevée). La suite va consister à établir la forme de la caractéristique électrique de sortie en tenant compte des contraintes physiques et de l'influence des différents paramètres physiques et électriques.

#### III.4. Caractéristique IDS(VDS) d'un transistor NMOS à enrichissement de canal :

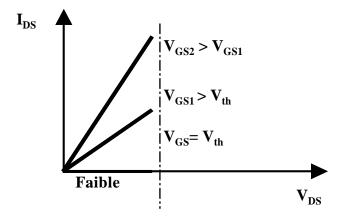

#### III.4.1. La tension drain-source $V_{DS}$ est faible

**Figure I.7 :** La variation de la résistance interne du transistor vue entre le drain et la source En fonction de V<sub>GS</sub>

Dès que la tension de grille atteint une tension de seuil appelée (threshold voltage)  $V_{TH}$ , le canal d'électrons est formé. Lorsque la tension  $V_{GS}$  croit encore, la densité d'électrons dans la zone de canal augmente et la résistance équivalente du canal diminue. La pente  $I_{DS}/V_{GS}$  augmente. Tant que la tension  $V_{DS}$  est faible, elle ne modifie sensiblement pas cette distribution de concentration d'électrons. Le dispositif est dit *en régime ohmique*; le transistor se comporte comme une résistance pilotée par la tension de grille (Figure I.7).

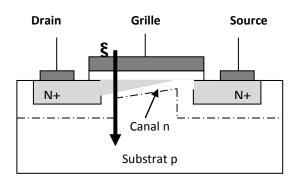

#### III.4.2. La tension de grille $V_{GS} > V_{TH}$ et la tension drain-source $V_{DS}$ non négligeable

$V_{GS}>V_{TH}$  signifie que pour la tension  $V_{DS}$  très faible, le canal d'électrons existe en tout point compris entre les zones de drain et de source. Pour une valeur de  $V_{DS}$  positive et non négligeable, la différence de potentiel entre la grille et le substrat (dans la zone de canal) coté drain diminue.

Cela revient à diminuer le champ électrique dans la zone de canal sous la grille, coté drain. La concentration dans le canal, du coté drain, a alors tendance à diminuer (Figure I.8). La résistance du canal coté drain augmente puisque le nombre de porteurs diminue, ce qui signifie que la pente de la courbe  $I_{DS}(V_{DS})$  diminue.

**Figure I.8 :** Modification de la forme du canal d'électron lorsque la tension de grille est supérieure à la tension de seuil et la tension de drain augmente. Le canal est beaucoup plus étroit du coté drain, jusqu'à ce qu'il disparaisse.

Nous dirons que nous sommes dans la zone de caractéristique intermédiaire, telle que représentée Figure I.9.

**Figure I.9 :** Evolution de la caractéristique  $I_{DS}(V_{GS})$  lorsque la tension de drain augmente, pour une tension de grille supérieure à la tension de seuil.

La conduction est alors assurée par le champ électrique transverse tel que présenter dans la Figure I.10.Notons que ce champ peut être calculé par intégration de l'équation de Poisson dans ce domaine compris entre l'extrémité du canal et la zone de drain

Si la concentration de dopant dans la zone de canal n'est pas trop faible, l'extension de cette zone est faible et la variation relative de la longueur totale du canal est faible. Le canal existant n'est alors pas modifié sensiblement et sa résistance entre la source et le point de pincement est pratiquement constante. Le potentiel du point de pincement correspond à  $V_{GS} - V_{TH}$  qui est constant pour une valeur donnée de  $V_{GS}$ . Ainsi, la différence de potentiel entre le point de pincement et la source est constante.

**Figure I.10 :** Déplacement du point de pincement lorsque la tension de drain rend la différence de potentiel entre grille et drain inférieure à la tension de seuil.

Différence de potentiel et résistance fixées, signifient que le courant traversant le canal,  $I_{DS}$ , est constant à  $V_{GS}$  donnée (I = U/R). La caractéristique électrique est alors *horizontale* et a l'allure de la Figure I.8. Nous dirons que le transistor est en *régime de saturation*. Pour un  $V_{GS}$  donné, la caractéristique de sortie comprend ainsi trois zones significatives :

- le régime ohmique.

- le régime intermédiaire.

- le régime de saturation.

Le point de saturation dépend de la valeur de  $V_{GS}$  puisqu'il apparaît pour  $V_{GS} - V_{DS} = V_{TH}$ . Cette valeur de  $V_{DS}$  s'appelle tension de saturation  $V_{DSsat}$ .

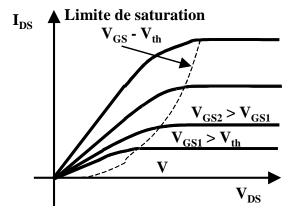

#### III.5. Caractéristique de sortie du transistor I<sub>DS</sub> (V<sub>DS</sub>, V<sub>GS</sub>)

La Figure I.8 a été tracée pour une tension appliquée sur la grille bien définie et supérieure à la tension de seuil. La modification de  $V_{GS}$  va :

- modifie la pente en régime ohmique,

- déplace la tension de saturation,  $V_{DSAT}$ ,

- modifie l'amplitude du courant de saturation.

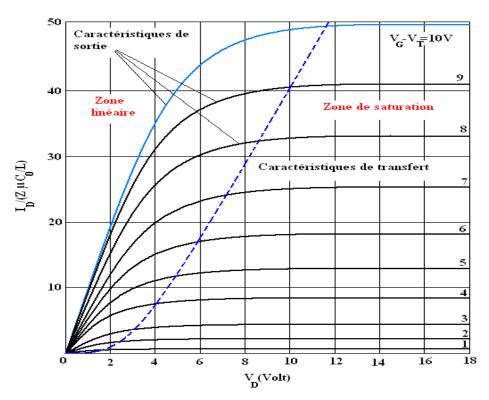

On retrouve de la sorte un réseau de courbes représenté dans la Figure I.11, semblable à celui d'un transistor bipolairemais la grandeur de contrôle est dans ce cas le potentiel de grille à la place du courant base.

Figure I.11 : Caractéristique de sortie du transistor MOS

#### IV. Analyse physique de la structure métal/oxyde/semi-conducteur idéale :

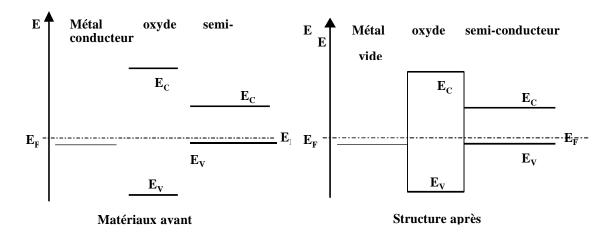

#### IV.1. Diagramme d'énergie à l'équilibre thermodynamique

La structure Métal/Oxyde/Semi-conducteur est donc un sandwich de couches constituées de matériaux de nature différente: conducteur, isolant

et semi-conducteur. Nous allons pour simplifier l'étude considérer que ces matériaux sont homogènes et ont des travaux de sortie identiques.

En d'autres termes, l'écart énergétique entre le niveau du vide et le niveau de Fermi du métal est égal à celui du semi-conducteur dopé constituant le substrat. A l'équilibre thermodynamique, il n'y a donc pas de différence de potentiel et donc pas de champ électrique local entre le conducteur et le semi-conducteur. La Figure I.12 montre les diagrammes d'énergie avant et après contact entre les différents matériaux. Nous considérerons toujours un modèle unidimensionnel : l'orientation est perpendiculaire aux interfaces.

**Figure I.12 :** Diagrammes d'énergie à l'équilibre thermodynamique des différents matériaux de la structure MOS avant contact puis après contact.

<u>NB</u>: Le niveau de Fermi est dans la bande de conduction pour le métal. La largeur de la bande interdite de l'oxyde est très grande devant celle du semi-conducteur. Le semi-conducteur est dopé p dans cet exemple, le niveau de Fermi se trouve donc proche de la bande de valence.

A l'équilibre thermodynamique, le métal et le semi-conducteur sont au même potentiel, les niveaux de Fermi sont donc alignés. Nous allons prendre comme potentiel de référence le potentiel du semi-conducteur loin de l'interface oxyde/semi-conducteur.

#### IV.2. Régime d'accumulation

Pour ce régime, une tension est appliquée sur le métal par rapport au semiconducteur qui correspond à la tension de grille appliquée par rapport au substrat. La chute de potentiel va se répartir entre l'oxyde et le semiconducteur près de l'interface. L'oxyde étant supposé idéal, il n'existe aucune charge à l'intérieur, ni statiques, ni en transit. D'après l'équation de Poisson, le champ électrique y est constant la variation de potentiel linéaire. Puisqu'il existe une charge d'espace possible dans le semi-conducteur, le champ peut varier dans cette zone, le potentiel aussi.

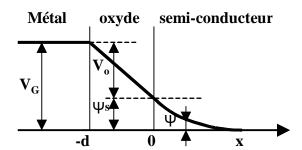

La Figure I.13 montre de façon qualitative la variation du potentiel dans la structure, et donc la variation du niveau du vide. Sur cette figure, nous appelons :

$-\psi_s$ : le potentiel à l'interface.

$-V_o$ : la chute de potentiel dans l'oxyde,

-  $\psi$ : le potentiel à l'abscisse x.

Figure I.13: variation du potentiel à travers la structure.

La variation est linéaire dans l'oxyde.  $\psi$ s est le potentiel à l'interface. Le potentiel de la grille est égal à la somme des potentiels dans l'oxyde et le semi-conducteur.

Lorsque  $V_G$  est négatif,  $\psi$  l'est aussi. Le niveau de Fermi dans la zone considérée se rapproche de la bande de valence. Notons la relation :

$$V_G = V_0 + \psi_S \tag{1.I}$$

Et comme:

$$p = N_V \exp(\frac{E_F - E_V}{KT}) \tag{2.1}$$

Le semi-conducteur s'enrichit en trous majoritaire, nous appelons ce régime le *régime d'accumulation*.

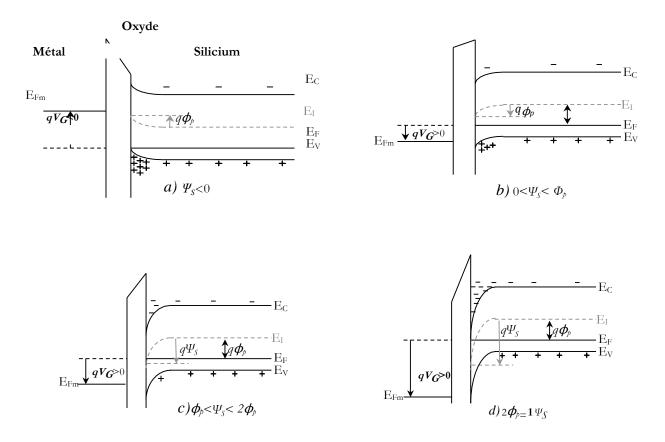

La zone de charge d'espace est alors remplie par des trous majoritaires et les concentrations des autres types de charges deviennent négligeables. La Figure I.14.a montre le diagramme d'énergie dans ce régime. Dans le cas présenté, le potentiel du métal est plus faible que celui du semi-conducteur (sens inverse des énergies).

**Figure I.14 :** Diagramme de bandes d'énergies pour un MOSFET à Canal n à désertion. MOSFET en régime a) accumulation b) désertion; c) inversion faible; d) inversion forte.

#### IV.3. Régime de désertion

Dans ces conditions, la tension appliquée sur le métal est positive :  $V_G>0$ , mais pas trop élevée. La courbure des bandes d'énergie est changée de sens par rapport au cas précédent. Le potentiel de surface,  $\psi$ s, est positif et donc le niveau de Fermi à l'interface s'éloigne de la bande de valence et se rapproche du milieu de la bande interdite, c'est-à-dire du niveau de Fermi intrinsèque. Il y a appauvrissement de porteurs, en trous dans cet exemple. La zone de charge d'espace contient principalement des atomes dopants ionisés (accepteurs dans ce cas).

La Figure I.14.b montre le diagramme d'énergie dans ces conditions. Il faut analyser la position du niveau de Fermi à l'interface oxyde-semi-conducteur. Dans ce cas

$$|q\psi_{s}| < |\phi_{p}| \tag{3.I}$$

Ce qui signifie que le niveau de Fermi reste dans la partie inférieure de la bande interdite. La concentration en trous est très inférieure à la concentration en dopant et la concentration en électrons reste complètement négligeable. La zone de charge d'espace s'étend en fonction de la tension appliquée sur la grille. Quand la courbure augmente, l'extension augmente.

#### IV.4. Régime de faible inversion

La tension appliquée sur le métal est plus élevée de manière à ce que le potentiel de surface (en énergie) soit supérieur à l'écart énergétique entre le niveau de Fermi et le niveau de Fermi intrinsèque dans le substrat semi-conducteur initial,  $q\phi_p$ .

Dans ces conditions, telles que représentées dans la Figure I.14.c, la courbure est vers le bas, le niveau de Fermi à l'interface est passé au-dessus du niveau de Fermi intrinsèque ; le niveau de Fermi à l'interface est plus proche de la bande de conduction que de la bande de valence. Les électrons sont alors plus nombreux que les trous mais restent néanmoins en

concentration négligeable par rapport aux atomes dopants ionisés. La population de porteurs s'est inversée à l'interface. Nous appelons ce régime la faible inversion.

#### IV.5. Régime de forte inversion

Ce régime débute lorsque le canal tel que nous l'avons défini commence à exister, c'est-à-dire dans le cas proposé, lorsque la concentration en électrons devient égale en surface du semi-conducteur à la concentration d'atome dopant ionisé, ce qui correspond à la concentration en trous dans le volume neutre (loin de l'interface). Dans ces conditions, l'écart énergétique entre le niveau de Fermi de surface et le niveau de Fermi intrinsèque est égal en valeur absolue à celui du volume neutre. Autrement dit, le potentiel en surface est égal ou supérieur à 2 fois  $\phi_p$ .

Nous noterons:

$$|\psi_s| \ge 2\phi_p \tag{4.1}$$

Lorsque:

$$|\psi_S| = 2\phi_n \tag{5.I}$$

Alors:

$$|V_G| = |V_{th}| \tag{6.1}$$

C'est-à-dire que la tension de grille est égale à la tension de seuil. La Figure I.15 montre cette situation. La courbure de bande a augmenté et la zone de charge d'espace atteint pratiquement un maximum.

En effet, la zone de charge d'espace comporte deux parties chargées avec des éléments portant le même signe :

- la zone désertée de concentration,  $N_A$  dans notre cas,

- la zone de canal de concentration n très élevée et supérieure à  $N_A$ .

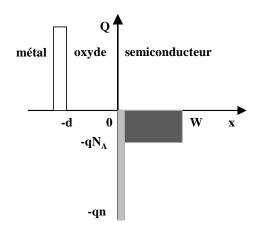

La zone de canal est en fait très fine (quelques Angström à quelques dizaines d'Angström) puisque les porteurs s'agglutinent contre la paroi d'oxyde. La charge totale de ces deux contributions se retrouve de signe opposé sur la grille comme le montre la Figure I.15.

**Figure I.15 :** Représentation de la distribution des charges dans la structure en régime de forte inversion.

Sur cette figure, très schématisée, il est possible de se rendre compte de la faible épaisseur du canal. Du coté du métal, la concentration en électrons est tellement forte que l'épaisseur concernée, correspondant à un déficit d'électrons est presque nulle.

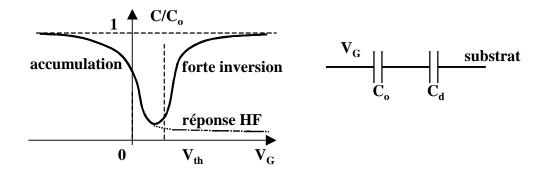

# IV.6. Capacité équivalente de la structure MOS :

On associe la variation de charge totale de la zone de charge d'espace à la variation de la tension de grille  $V_G$ , par l'équivalence d'une capacité :

$$C = \frac{dQ_S}{dV_G} \tag{7.I}$$

Or on sait que:

$$V_G = V_{o+} \Psi_s \text{ et donc } dV_G = dV_{o+} d\Psi$$

(8.1)

Et donc:

$$V_G = dV_0 + d\psi_s \tag{9.1}$$

D'où:

$$C = \frac{dQ_S}{dV_0 + d\psi_S} = \frac{1}{\frac{dV_0}{dQ_S} + \frac{d\psi_S}{dQ_S}}$$

(10.I)

Le premier terme du dénominateur correspond à la capacité de l'oxyde *Cox*. Le second à la capacité équivalente de la zone de charge d'espace du semi-conducteur, *Cd*.

$$C = \frac{1}{\frac{1}{dC_{OX}} + \frac{1}{dC_{d}}} = C = \frac{C_{OX}C_{d}}{C_{OX} + C_{d}}$$

(11.I)

La capacité totale est équivalente à la mis en série des deux capacités  $C_{ox}$  et  $C_d$ . Peut être déduit de l'étude de  $Q_s(\psi_s)$ , pente de la courbe. Ainsi, si nous supposons que la variation de Vg est suffisamment lente pour considérer que l'équilibre est atteint en permanence, la forme de  $C(V_G)$  est celle représentée sur la Figure I.16. Pour effectuer la mesure il faut en général superposer à  $V_G$  un signal variable. En haute fréquence, les porteurs minoritaires ne peuvent pas suivre la variation imposée, puisqu'ils sont trop peu nombreux pour permettre d'atteindre l'équilibre. Pour des zones de substrat de très bonne qualité (grande durée de vie), le domaine de « haute fréquence » peut débuter à quelques dizaines de Hertz.

**Figure I.16 :** Variation de la capacité normalisée en fonction de la tension de grille

La capacité totale est la mise en série des deux capacités  $C_o$  et  $C_d$ . Si la fréquence est très basse, les porteurs minoritaires ont le temps de répondre et la capacité remonte vers Co en forte inversion. En haute fréquence, nous obtenons la courbe en pointillés pour les tensions de grille positives.

# V. Caractéristique d'un transistor MOS idéal

Il s'agit de retrouver les expressions analytiques  $I_D(V_{DS}, V_{GS})$  correspondant à la forme de la caractéristique présentée au *paragraphe 2*. Cela va nécessiter un certain nombre d'approximations en fonction du régime de fonctionnement. Nous nous limiterons à ce stade, à la caractéristique en conduction, c'est-à-dire pour des tensions de grille au moins égales, en valeur absolue, à la tension de seuil.

# V.1. Expression de la charge dans le canal

La charge totale dans le semi-conducteur,  $Q_s$ , est la somme de la charge correspondant aux atomes dopants ionisés dans la zone de charge d'espace,  $Q_B$ , et de la charge équivalente des porteurs libres dans le canal,  $Q_I$ . Ainsi :

$$Q_S = Q_I + Q_B \tag{12.I}$$

La tension de grille,  $V_G > V_{TH}$  est appliquée sur une face de l'isolant. En raisonnant à l'aide d'un condensateur équivalent, la charge totale  $Q_s$  se retrouve en vis-à-vis aux bornes de l'isolant. La tension aux bornes de l'isolant s'exprime alors par :

$$V_0 = -\frac{Q_S}{c_{ox}} \tag{13.I}$$

Et donc:

$$V_G = -\frac{Q_S}{C_{ox}} + \psi_S \tag{14.I}$$

Lorsque  $V_G = V_{TH}$ , nous pouvons supposer que  $Q_I$  est encore négligeable puisque le canal commence tout juste à se former ; même si la concentration des porteurs atteint celle du dopage, l'épaisseur du canal est encore suffisamment faible pour être négligeable devant l'extension de la zone de charge d'espace ; ceci est bien sûr une approximation importante. Alors :

$$V_G = -\frac{Q_B}{C_{ox}} + 2\phi_p \tag{15.I}$$

Ainsi, en tout point du canal, le potentiel est  $V_G - V_{TH} - \Delta \psi$ , ce dernier terme représentant le potentiel local dans la zone de canal à l'interface oxyde-semi-conducteur.

**Figure I.17 :** Représentation schématique de la structure MOS en régime de conduction non saturée

Le canal couvre toute l'interface. Le potentiel de surface varie en fonction de la position y ; il en est de même pour la charge d'interface  $Q_I$ . L'intégrale de la résistance entre 0 et L permet de déterminer le courant total drain-source traversant le transistor. La résistance augmente proportionnellement avec la polarisation drain-source.

#### V.2. Calcule du courant

Dans la zone de canal quand celui-ci existe, nous ne supposons que le mécanisme de conduction prépondérant est de type dérive dans le champ électrique transverse,  $\xi_y$ . L'expression du courant inclue donc le champ électrique, la mobilité des porteurs, la charge du canal par unité de surface, et la largeur du canal, W. La longueur du canal est L.

$$I_D = -W\mu_n Q_I \xi_y \text{ et } \xi_y = -\frac{d\psi}{dy}$$

(16.I)

Donc:

$$I_D = -W\mu_n C_{ox} (V_G - V_{TH} - \psi(y)) \frac{d\psi}{dy}$$

(17.I)

En intégrant cette équation tout le long du canal entre 0 et L, le potentiel variant de 0 à  $V_D$ .

$$\int_{0}^{L} I_{D} \, dy = W \mu_{n} C_{ox} \int_{0}^{V_{D}} (V_{G} - V_{th} - \psi) \, d\psi$$

(18.I)

$$I_D L = W \mu_n C_{ox} \left[ (V_G - V_{TH}) V_D - \frac{V_D^2}{2} \right]$$

(19.I)

D'où:

$$I_D = \frac{W}{L} \mu_n C_{ox} \left[ (V_G - V_{TH}) V_D - \frac{V_D^2}{2} \right]$$

(20.I)

L'expression du courant trouvée ici est très simplifiée mais donne un bon aperçu de l'équation de la caractéristique du transistor. Sans les approximations, la résolution est beaucoup plus compliquée.

Dans le calcul ci-dessus, nous avons supposé que le canal existe sur toute la longueur L en régime limite. Lorsque  $V_{DS} = V_{GS} - V_{TH}$ , le point de pincement du canal apparaît au niveau du drain.

Cette situation correspond au début de la saturation du courant ; le courant de saturation sera noté  $I_{DSAT}$ .

D'autre part on a que :  $V_{Dsat} = V_G - V_{TH}$

D'où:

$$I_D = \frac{W}{L} \mu_n C_{ox} \left[ (V_G - V_{th}) V_D - \frac{(V_G - V_{TH})^2}{2} \right]$$

(21.I)

À la fin on aboutie à :

$$I_D = \frac{W}{L} \mu_n C_{ox} \frac{(V_G - V_{TH})^2}{2}$$

(22.I)

Ainsi, nous déterminons le courant de saturation qui ne dépend que de la différence entre la tension de grille et la tension de seuil.

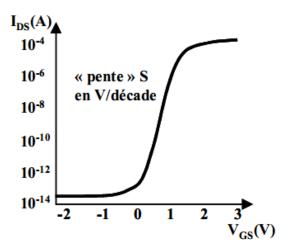

Il faut cependant remarquer que pour la tension de grille très légèrement inférieure ou égale à la tension de seuil, le courant n'est pas nul. Pour connaître le comportement électrique au-dessous du seuil, il faut reprendre les équations qui déterminent la quantité effective des porteurs (dans notre cas les électrons) dont la concentration est inférieure à la concentration de dopant mais est loin d'être nulle (1017cm-3 par exemple). Dans ces conditions, nous déterminons la caractéristique de transfert sous le seuil, le courant pouvant varier sur une bonne dizaine de décades pour atteindre la valeur du courant inverse d'une des deux jonctions drain-canal ou source-canal.

La forme de cette caractéristique et plus particulièrement sa pente dans une échelle logarithmique est directement liée à l'épaisseur d'oxyde, au dopage de la zone de canal et à la densité de charge parasite liée essentiellement aux défauts d'interface oxyde/zone canal.

**Figure I.18 :** Caractéristique de transfert typique d'un transistor NMOS intégré

Le courant drain-source varie sur une dizaine de décade pour une variation de l'ordre du volt pour la tension de grille.

On peut conclure alors ce qu'on a vue précédemment par le Réseau de caractéristiques présenter dans la Figure I.19 :

**Figure I.19 :** Réseau de Caractéristiques I(V) d'un MOSFET idéal.

# VI. Modèle petit signal du MOSFET en saturation sans effet de substrat du MOS

Il se trouve que dans ce modèle Le courant IDS peut être exprimé par :

$$I_D = g_m V_{GS} + g_{DS} V_{DS} + g_{mb} V_{BS} (23.1)$$

On défini alors La conductance  $g_{\scriptscriptstyle D}$  et la transconductance  $g_{\scriptscriptstyle m}$  par :

$$g_{DS} \equiv \frac{\partial I_D}{\partial V_{DS}} \Big\{ V_{GS} = cons \cong \frac{W}{L} \mu_n C_{ox} (V_G - V_{TH})$$

(24.I)

$$r_{DS} = \frac{1}{\lambda I_{D0}} \tag{25.I}$$

$$g_m \equiv \frac{\partial I_D}{\partial V_{GS}} \Big\{ V_{DS} = cons \cong \frac{W}{L} \mu_n C_{ox} V_D$$

(26.I)

$$g_{mb} = \frac{\partial I_{DS}}{\partial V_{BS}} = \frac{\gamma}{2\sqrt{2|\phi_F|} + V_{SBQ}} \cdot g_m \tag{27.I}$$

On en déduit alors le schéma équivalent du MOSFET en régime petits signaux qui est donné par le schéma de la Figure(I.20)

**Figure I.20** Schéma équivalent du MOS en régime petits signaux sans effet de substrat.

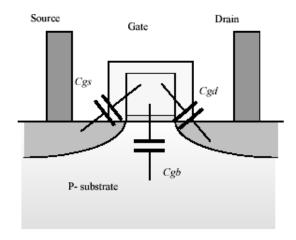

# VI.1. Capacités du MOS

En haute fréquence les modèles du MOS que nous avons cité sont inadéquats. Cette limitation est en fait due aux capacités parasites inhérentes à la structure MOS.

La plupart des capacités du modèle petits signaux sont facilement déduits du modèle physique des transistors MOS

Figure I.21: Capacités de terminaison du MOS

Sur le tableau ci-dessous nous indiquons pour chacune des zones de fonctionnement du MOS les valeurs de capacités de terminaison en fonction des capacités intrinsèques.

| Region   |                  |                                      |                                      |

|----------|------------------|--------------------------------------|--------------------------------------|

|          | Bloquée (cutoff) | ohmique                              | saturée                              |

| $C_{GD}$ | $C_{ox}WL_{D}$   | $C_{ox}WL_{D} + \frac{1}{2}WLC_{ox}$ | $C_{ox}WL_{D}$                       |

| $C_{GS}$ | $C_{ox}WL_{D}$   | $C_{ox}WL_{D} + \frac{1}{2}WLC_{ox}$ | $C_{ox}WL_{D} + \frac{2}{3}WLC_{ox}$ |

| $C_{BG}$ | $C_{ox}WL$       | 0                                    | 0                                    |

| $C_{BD}$ | $C_{BD1}$        | $C_{BD1} + \frac{1}{2}C_{BC1}$       | $C_{BD1}$                            |

| $C_{BS}$ | $C_{BS1}$        | $C_{BS1} + \frac{1}{2}C_{BC1}$       | $C_{BS1} + \frac{2}{3}C_{BC1}$       |

**Tableau I.1 :** les valeurs de capacités de terminaison en fonction des capacités intrinsèques

#### VI.2. Modèles du MOS Utilisés en simulation

# VI.2.1. Régime d'inversion du transistor MOS

Selon la valeur de  $V_{GS}$ , le canal du MOS est plus au moins bien formé. On peut distinguer trois types d'inversion, l'inversion faible correspondant a l'absence de canal mais pour la quelle il existe néanmoins des porteurs de courant en faible quantité dans la zone de charge d'espace engendré par la présence d'un canal fortement rempli de porteurs du courant (électrons pour un NMOS et trous pour un PMOS) et entre les deux l'inversion modérée ou le canal est présent mais ou la quantité de charges mobiles dans le canal n'est pas prédominante devant la située sous le canal.

- $V_{TH} (50 \text{ à } 100 \text{mV} < V_{GS} < V_{TH})$ : Inversion faible

- $V_{TH} < V_{GS} < V_{TH} + (75 à 100 mV)$ : Inversion modérée

- $V_{GS} > V_{TH} + 100 \, mV$ : Inversion forte

#### VII. Effet des canaux courts des transistors MOSFET

#### VII.1. Définition

La diminution de la longueur des canaux des transistors MOSFET induit de nombreux effets. Tel que les effets d'ionisation par impact, saturation de la vélocité, dégradation de la mobilité......On s'intéresse particulièrement dans ce qui suit à un de ces effets appelé effet des canaux courts.

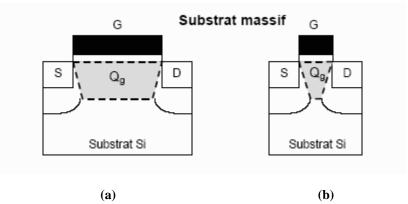

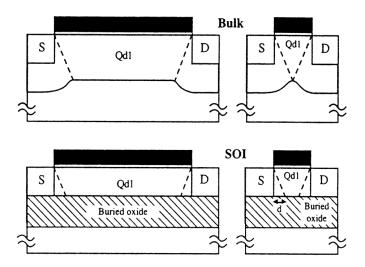

Ces effets sont dus aux zones de désertion de la source et du drain qui viennent recouvrir partiellement la zone de la grille représentée par le trapèze  $Q_g$ . Ceci est bien représenté sur le schéma de la figure qui suit :

**Figure I.22 :** Distribution de la charge de désertion contrôlée par la grille (Qg) pour (a) un MOSFET à canal long, (b) un MOSFET à canal court.

Pour de long transistor cet effet est insignifiant par rapport à la zone de contrôle de la grille. Cet effet devient de plus en plus significatif au fur et à mesure que la longueur du canal diminue.

# VII.2. Impact sur la tension de seuil

Les effets des canaux courts ont un impact important sur les caractéristiques statiques du MOSFET. Par exemple ces effets dégradent la

pente sous seuil et par conséquent la vitesse de commutation des circuits numériques. Ils détériorent également le courant de fuite à l'état bloqué et peuvent impliquer une conduction du transistor sous la tension de seuil. De ce fait les paramètres technologiques ont un impact direct sur la tension de seuil.

Par exemple, l'effet *DIBL* qu'on expliquera par la suite augmente lorsque la longueur de la grille diminue.

Le courant de drain dans ces transistors à canaux courts augmente considérablement avec la tension de drain au-delà de la zone de pincement (saturation) en comparaison avec des dispositifs dits à canal long où l'on peut considérer que le courant reste constant en saturation (si on néglige l'effet Early). C'est comme si courant de drain d'un transistor à canal court ne sature pas vraiment Figure I.23

**Figure I.23 :** Caractéristiques  $I_D/V_D$  d'un transistor MOS à canal court  $(L=0.23 \mu m)$  [SZE81]

En outre, le courant de drain n'est pas nul pour une tension  $V_{GS}$  nulle. Pour une tension de drain de l'ordre de 3V pour un transistor d'une longueur de 0.23µm par exemple comme illustré en Figure I.23 [SZE81], le courant de drain peut atteindre le milliampère. La grille a donc perdu le contrôle du canal et ne peut plus "couper" le transistor.

En deuxième lieu, considérons la caractéristique  $I_D/V_G$  de transistors MOS à canal court en régime sous seuil représenté en Figure I.24.

**Figure I.24 :** Caractéristiques I<sub>D</sub>/V<sub>G</sub> du transistor MOS en régime sous seuil Pour différentes longueurs de canal. [YAU74]

La caractéristique  $I_{DS}$ =  $f(V_{GS})$  est idéale pour des transistors à canal long, Ceci est bien illustré dans le cas de la Figure I.24.

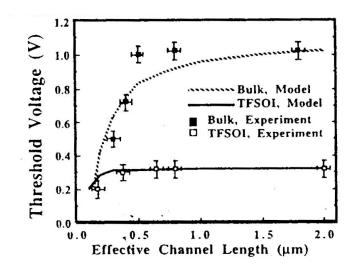

En faisant alors varier la longueur du canal de  $0.8\mu$  à  $5\mu$  notre caractéristique se déforme lorsque L devient inférieur à  $2\mu m$ . On se trouve donc en présence d'une chute de la tension de seuil lorsque la longueur de canal diminue en dessous de  $2\mu m$ . En dessous de  $0.8\mu m$ , la tension de grille ne contrôle plus le courant de drain et le transistor ne peut plus être utilisé alors comme interrupteur [YAU74].

La variation de la tension de seuil avec la variation de la longueur du canal est représentée sur la Figure I.25 [SZE80].

**Figure I.25 :** Evolution de la tension de seuil en fonction de la longueur du canal [SEI80].

On peut donc conclure que pour les dispositifs à canaux longs, la tension de seuil est indépendante de la longueur de canal. Toutefois, pour les transistors à canal court, la tension de seuil décroît fortement lorsque L devient inférieur à 2µm [SEI80].

# VII.3. Effets d'ionisation par impact

L'expression du champ électrique longitudinal dans la région de pincement est donnée par l'équation :

$$E(x) = E_{sat} \cosh\left(\frac{x - L_{sat}}{l_P}\right)$$

(28.I)

Où:

$$l_p = \sqrt{\frac{\varepsilon_s}{c_{ox}} t_d} \tag{29.I}$$

#### Avec:

- *L*<sub>sat</sub> est la longueur du canal jusqu'au point de pincement.

- $L_p$  est la longueur caractéristique

- $T_d$  est l'épaisseur de la région  $n^+$  de drain pour un MOSFET à substrat massif.

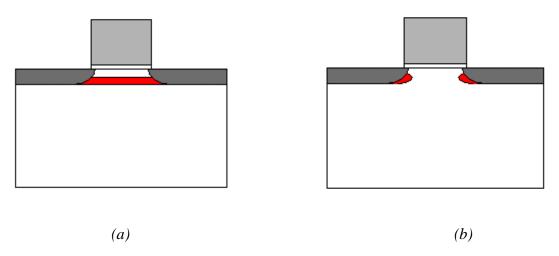

A la jonction drain/canal, l'amplitude de ce champ électrique est maximale. Elle est notée Ed et dépends de  $L_g$  qui représente la longueur de la grille et de  $V_{ds}$  .l'amplitude eu champs électrique est à ce niveau supérieur à l'amplitude du champ électrique critique noté  $E_c$ , lié à la vitesse de saturation des porteurs. Pour des transistors à canal long  $E_c$  se situe prés du point de pincement. Lorsque la longueur du canal diminue,  $E_c$  se rapproche de la jonction source/canal. Lorsque les porteurs minoritaires atteignent leur vitesse de saturation, le champ électrique longitudinal continue à céder de l'énergie à ces porteurs.

Les interactions dans le réseau cristallin modifie aléatoirement leur libre parcours moyen puisque leur vitesse de propagation reste constante, par conséquent leur énergie cinétique augmente, en suivant une loi de probabilité dictée par les interactions dans le canal ce qui est bien illustré dans la figure qui suit :

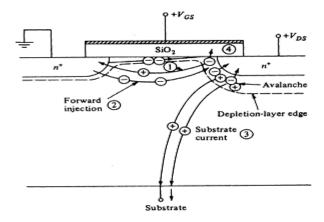

**Figure I.26 :** schématisation du phénomène d'ionisation par impact dans un transistor à canal N.

Une partie de ces porteurs ont une énergie suffisamment importante pour ioniser les atomes de silicium du cristal. Ils sont appelés les porteurs chauds. Des paires électrons/trous se forment à partir de ces impacts. Le champ électrique longitudinal attire les électrons du coté du drain. Les trous sont repousses vers le substrat par le champ électrique de la zone de désertion. Ces trous, issus de l'ionisation par impact, constituent le courant de substrat. Ce dernier a pour expression :

$$I_{db} = |I_{ds}|K_i(V_{ds} - V_{dsat})exp\left(\frac{V_i}{V_{th} - V_{dsat}}\right)$$

(30.I)

Où :  $K_i$  et  $V_i$  sont des paramètres empiriques d'ajustement.

Le rapport  $\left(\frac{l_{db}}{l_{ds}}\right)$  représente le coefficient d'ionisation par impact. Une partie des électrons dans le canal, possède une énergie suffisante pour franchir la barrière de potentiel située entre l'oxyde de grille et la zone active. Ces électrons sont ensuite collectés par la grille. Ces électrons forment ainsi un courant de grille. Une portion de ces électrons dégrade l'interface oxyde de grille/ substrat et augmente alors la densité d'état d'interface. La mobilité diminue (dégradation de la mobilité) alors que la tension de seuil augmente. Une partie des électrons issus du canal se trouve piégés dans l'oxyde. Ce piégeage a pour effet d'augmenter la quantité de charge intrinsèque de l'oxyde de grille.

# VII.4. Effets thermiques

Lors du fonctionnement du transistor la puissance électrique génère une quantité de chaleur par effet joule. Plus cette puissance sera élevée, plus la température du canal augmentera. Il est à noter que la mobilité, la tension de seuil et la vitesse de saturation dépendent étroitement de la température par les relations qui suivent :

$$\mu_{eff} = \mu_{eff}_{T_{amb}} \left(\frac{T}{T_{amb}}\right)^{-k1} \tag{31.I}$$

$$V_{th} = V_{theff_{T_{amb}}} - k2(T - T_{amb})$$

(32.I)

$$v_{sat} = v_{sat}_{T_{amb}} - A_T \left( \frac{T - T_{amb}}{T_{amb}} \right)$$

(33.I)

Où:

- $k_1 \in [1.5; 1.7]$ .

- $k_2 \in [0.5; 4]$ .

- $A_T = 3.3 \ 10^4$ .

$\mu_{eff_{T_{amb}}}$ ,  $V_{theff_{T_{amb}}}$  et  $v_{sat_{T_{amb}}}$  Sont respectivement la mobilité effective, la tension de seuil effective et la vitesse de saturation effective à la température ambiante  $T_{amb}$ . La réduction de la mobilité effective est le facteur limitatif dominant. Lorsque la température ou la puissance dissipée augmente, la mobilité diminue entrainant la décroissance du courant  $I_{DS}$ . Ainsi la puissance dissipée sera plus faible, ce qui va entrainer la diminution de la température. Un phénomène auto entretenu est alors mis en place reliant la température du canal et le courant du drain. Cet effet est l'effet d'auto-échauffement. E, conséquence la caractéristique  $I_{DS}=f(V_{GS})$  présente en mode saturé une décroissance.

# VII.5. Les avantages des transistors MOS :

• Sa résistance d'entrée est très importante  $R_s\approx 10^{12}\Omega$  , pour un transistor à effet de champ à jonction, elle est plus faible, soit de l'ordre de  $10^8\Omega$  .

- le bruit intrinsèque est toujours très faible.

- Facile à fabriquer et par suite peu onéreux.

- La densité d'intégration autorisée par ce type de composant est très importante: (10<sup>7</sup> transistors sur une seule puce).

- Petite surface de silicium

- Impédance de sortie faible de l'ordre de  $100\Omega$ .

- Ce composant est symétrique, aucune distinction du point de vu fabrication entre la source et le drain.

- le circuit de commande très simple.

- Il supporte très bien la mise en parallèle sans dispositif particulier grâce à son coefficient de température positif.

#### VIII. Conclusion

Nous avons présenté au sein de ce chapitre les transistors MOSFET pour les quels nous avons expliqué le mode de fonctionnement dégageant ainsi leurs caractéristiques électriques. Les effets indésirables les plus dominantes dans les transistors à canaux court sont aussi présentés dans cette section. On se propose d'étudier dans ce qui suit les courants de fuites dans un type de transistors à canaux court qui sera brièvement décrit par le passage.

# CHAPITRE - II ETUDE DES COURANTS DE FUITES DANS LES TRANSISTORS MOSFET

Avant de présenter les courants de fuite altérant le fonctionnement des transistors MOSFET submicronique, on propose un model de transistor MOSFET à canal court auquel nous nous sommes intéresse pour la détermination des courants de fuite, Ce transistor intitulé BSIM4, largement utilisé en industrie est la dernière conception de l'université de Californie de Berkeley.

#### I. Etude du model BSIM4:

#### I.1. Introduction

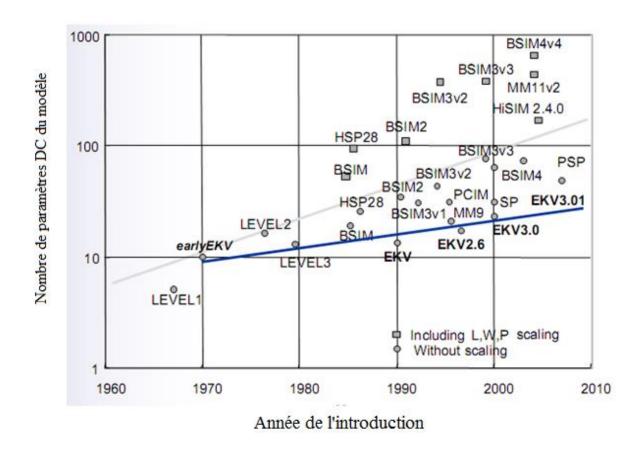

L'évoluions des modèles compacts :

**Figure II.1 :** Nombre de paramètres DC du modèle en fonction l'introduction du modèle [HAL.96].

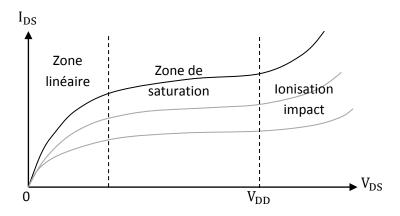

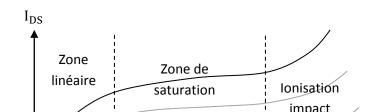

Une nouvelle manière de modéliser le MOS fait apparaître une nouvelle version appelée BSIM4 qui a été présenté en 2000. Le BSIM4 est un modèle qui prend toujours en considération les régions de fonctionnement décrites dans le niveau 3 du MOS (linéaire pour des tensions relativement basse de  $V_{DS}$ , saturé pour des tensions $V_{DS}$  relativement importantes, subliminal pour  $V_{GS}$  inférieures à la tension de seuil  $V_{th}$ ). Le BSIM4 présente non seulement, en plus de ses prédécesseurs, une continuité parfaite entre ses différentes régions de fonctionnement, mais en plus, une nouvelle région où l'effet d'ionisation par impact est dominant, cette région peut être mise en évidence pour des valeurs très importantes de la tension drain-source bien au-dessus de la tension d'alimentation nominale $V_{DD}$

La caractéristique théoriques  $I_{DS}$  en fonction de la tension $V_{DS}$  est celle de la Figure II.2.

Figure II.2 : Caractéristique  $I_{DS}$  en fonction de  $V_{DS}$ du modèle BSIM4