# Ministère de l'Enseignement Supérieur et de la Recherche Scientifique Université de Tlemcen Faculté de Technologie Département de Génie Électrique et Électronique

#### MÉMOIRE DE FIN D'ÉTUDE

pour obtenir le grade de

MASTER EN ELECTRONIQUE

Spécialité: Instrumentation Électronique

présenté et soutenu publiquement par

# Mohammed El Amine BRIXI NIGASSA & Mohammed Amine TABERKIT

le 27 Juin 2013

Titre:

# ÉTUDE ET RÉALISATION D'UN TESTEUR DE TEMPS DE RÉACTION

#### Jury

Président du jury. Dr. A.HAMDOUN, MCA UABB Tlemcen Examinateur. Dr. A.BELAID, MCA UABB Tlemcen Examinateur. Dr. S.SOULIMANE, MCA UABB Tlemcen Directeur de mémoire. Dr. A. BOUAZZA née Guen, MCA UABB Tlemcen

### Dédicaces

Au nom de Dieu, le clément, le très miséricordieux

Nous dédions ce travail

A nos chers parents qui nous ont épaulés et soutenus

dans tous ce qu'on a entrepris dans nos vies

A Nos adorables sœurs

A tous nos oncles et tantes sans exception

A tout nos cousins et cousines

A tous nos amis (es)

### Remerciements

Avant tout, il ne saurait question d'entreprendre les remerciements sans avoir remercié le BON DIEU de nous avoir permis de réaliser ce travail.

Nous tenons à remercier :

Tout d'abord à nos chers parents, d'avoir été là toutes ces années de nous avoir aidé à faire ce très long parcours, et de nous avoir guidé vers le droit chemin

Un grand merci à **Mme. A. BOUAZZA** : notre encadrant pour sa confiance en nous et pour son aide si précieuse qui nous a permis d'achever notre modeste travail.

Nous adressons aussi toute notre gratitude et respects envers **Mr. HAMDOUN**, qui nous a fait l'honneur de présider le jury de notre mémoire.

Notre gratitude et remerciements vont aussi à Mr. BELAID et Mr. SOULI-MANE, qui ont aimablement acceptés de juger ce travail.

Nous tenons à remercier tous les membres du Laboratoire de Recherche Génie Biomédical pour leurs soutiens inconditionnels et leur aide si précieuse qui a permis l'aboutissement de ce modeste travail.

Enfin, à toutes les personnes ayant participé de près ou de loin à la réalisation de ce projet, un grand merci.

### Résumé

Le temps de réaction est un paramètre important qui permet de renseigner sur l'état d'un individu donné. Dans ce cadre on se propose d'étudier "un testeur de temps de réaction",qui est en faite , réaliser un testeur dont le but sera de mesurer le temps que met un individu pour réagir à un voyant lumineux .

Les résultats obtenus sont satisfaisants et montrent la simplicité et l'éfficacité de notre testeur permettant de mesurer ce temps de réaction.

Mots clés Testeur, Temps de réaction, Automobile, réflexe.

### Abstract

The reaction time is an important parameter which allow to enquire about the status of a given individual. In this context we propose to study "A tester of reaction time", which is in fact, realize a tester whose purpose is to measure the time that takes individual to react to a bright indicator .

The results are satisfactory and show the simplicity and the effectiveness of our tester to measure the reaction time.

Keywords Tester, Reaction time, automobile, reflex.

## Table des matières

|    | Déd                  | caces                                                     |                |

|----|----------------------|-----------------------------------------------------------|----------------|

|    | Rem                  | erciements                                                | i              |

|    | Résu                 | mé                                                        | ii             |

|    | Abs                  | ract                                                      | iii            |

|    | Tabl                 | e des matières $\dots\dots\dots\dots$                     | iv             |

|    | Tabl                 | e des figures                                             | vii            |

|    | Liste                | des tableaux                                              | Х              |

| _  | _                    |                                                           |                |

| ln | trod                 | ction                                                     | 1              |

| 1  | $\operatorname{Sch}$ | ma synoptique et étude théorique                          | 2              |

|    | 1                    | Schéma fonctionnel du testeur de temps de réaction        | 2              |

|    | 2                    | Les Circuits multivibrateurs astables                     | 3              |

|    |                      | 2.1 Montages astables à base d'amplificateur opérationnel | 3              |

|    |                      | 2.2 Montages à portes logiques                            | 5              |

|    | 3                    | Les portes logiques                                       | 6              |

|    |                      | 3.1 L'inverseur                                           | 6              |

|    |                      | 3.2 La porte AND                                          | 6              |

|    |                      | 3.3 La porte NAND                                         | 7              |

|    |                      | 3.4 La porte OR                                           | 7              |

|    |                      | 3.5 La porte NOR                                          | 8              |

|    |                      | 3.6 La porte XOR                                          | 8              |

|    |                      | 3.7 La porte NXOR                                         | 9              |

|    | 4                    | Les bascules                                              | 9              |

|    |                      |                                                           | 10             |

|    |                      |                                                           | 11             |

|    |                      |                                                           | 12             |

|    |                      |                                                           | 13             |

|    | 5                    |                                                           | 14             |

|    |                      | -                                                         | 14             |

|    |                      | · · · · · · · · · · · · · · · · · · ·                     | 17             |

|    | 6                    | <u>.                                      </u>            | 18             |

|    | 7                    |                                                           | 20             |

|    |                      |                                                           | 20             |

|    |                      | <i>U</i> 1                                                | 20             |

|    |                      | 9                                                         | $\frac{1}{21}$ |

|    |                      | 9                                                         | $\frac{1}{21}$ |

|    | 0                    |                                                           | 00             |

| <b>2</b> | Prέ   | esentation, Etude et simulation du système                           | 23 |

|----------|-------|----------------------------------------------------------------------|----|

|          | 1     | Schéma Electrique du testeur de temps de réaction                    | 23 |

|          | 2     | Etude électrique du montage du testeur de temps de réaction          | 24 |

|          |       | 2.1 Présentation générale du Logiciel Proteus                        | 24 |

|          | 3     | Le générateur de base de temps                                       | 25 |

|          | 4     | Le diviseur de fréquence                                             | 27 |

|          | 5     | Le générateur d'impulsion en sortie du CD4040                        | 30 |

|          | 6     | Chronométrage du temps de réflexe :                                  | 37 |

|          | 7     | Quelques résultats obtenus en simulation                             | 38 |

|          |       | 7.1 L'affichage lors de l'initialisation                             | 38 |

|          |       | 7.2 Premier résultat de test sur simulation                          | 38 |

|          |       | 7.3 Deuxième résultat de test sur simulation                         | 39 |

|          | 8     | Conclusion                                                           | 39 |

| 3        | Réa   | alisation et résultats pratiques du testeur de temps de réaction     | 40 |

|          | 1     | Présentation de notre circuit finale sur circuit imprimé             | 40 |

|          | 2     | Prélèvement des différents signaux au niveau des noeuds de sortie de |    |

|          |       | notre testeur de temps de réaction                                   | 41 |

|          |       | 2.1 Signal prélevé à la sortie du circuit intégré NE555              | 41 |

|          |       | 2.2 Le signal à la sortie du circuit intégré CD4040                  | 42 |

|          |       | 2.3 Le signal à la sortie du dérivateur                              | 43 |

|          | 3     | Analyse du circuit :                                                 | 43 |

|          |       | 3.1 Le circuit de temporisation                                      | 43 |

|          |       | 3.2 Circuit de déclenchement                                         | 45 |

|          |       | 3.3 Chronométrage du temps de reflexe                                | 45 |

|          |       | 3.4 Comptage numérique                                               | 45 |

|          |       | 3.5 Affichage                                                        | 46 |

|          | 4     | Résultats et interprétations                                         | 46 |

|          | 5     | Conclusion                                                           | 49 |

| C        | onclu | ision et Perspectives                                                | 50 |

| Bi       | blio  | graphie                                                              | 51 |

| Aı       | nnex  | ces                                                                  | 53 |

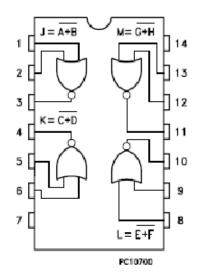

| Le       | e Cir | cuit Intégré CD 4001                                                 | 54 |

| Le       | e Cir | cuit Intégré CD 4011                                                 | 56 |

| Le       | e Cir | cuit Intégré CD 4060                                                 | 58 |

| Le       | e Cir | cuit Intégré CD 4511                                                 | 61 |

| Le       | e Cir | cuit Intégré NE555                                                   | 63 |

| Le       | Co    | mpteur Binaire CD 4040                                               | 68 |

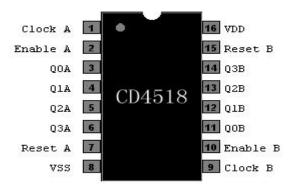

| Le       | Do    | uble Compteur BCD CD 4518                                            | 70 |

TABLE DES MATIÈRES V

L'Afficheur 7 segments LTS7760R

73

TABLE DES MATIÈRES VI

# Table des figures

| 1.1  | Schéma fonctionnel du testeur de temps de réaction                | 2  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Montages astables à base d'amplificateur opérationnel             | 3  |

| 1.3  | La charge et la décharge du condensateur du ontage astable à base |    |

|      | d'AOP                                                             | 4  |

| 1.4  | Montage astable à portes logiques                                 | 5  |

| 1.5  | La tension $V_{DD}$ en fonction de V1, V2 et V3. [1]              | 5  |

| 1.6  | L'inverseur. [2]                                                  | 6  |

| 1.7  | La porte logique AND. [2]                                         | 6  |

| 1.8  | La porte NAND. [2]                                                | 7  |

| 1.9  | La porte OR. [2]                                                  | 7  |

| 1.10 | La porte NOR. [2]                                                 | 8  |

|      | La porte XOR. [2]                                                 | 8  |

|      | La porte NXOR. [2]                                                | 9  |

|      | La Bascule RS                                                     | 10 |

| 1.14 | Le chronogramme de La Bascule RS                                  | 10 |

|      | La Bascule RSH                                                    | 11 |

|      | Le chronogramme de La Bascule RSH                                 | 12 |

|      | La Bascule JK                                                     | 12 |

| 1.18 | Le chronogramme de La Bascule JK                                  | 13 |

| 1.19 | La Bascule D                                                      | 14 |

|      | chronogramme de La Bascule D                                      | 14 |

| 1.21 | Compteur asynchrone modulo 8                                      | 15 |

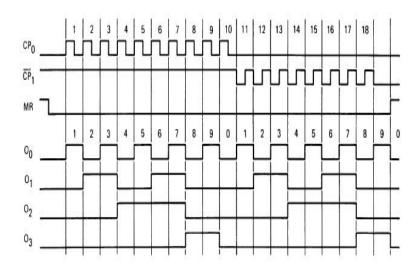

|      | chronogramme d'un compteur asynchrone modulo 8                    | 15 |

|      | chronogramme de la sortie Q0 du compteur asynchrone Modulo 8      | 17 |

|      | compteur synchrones Modulo 4                                      | 18 |

|      | Symbôle d'une diode Électroluminescente DEL                       | 18 |

|      | Diode Électroluminescente DEL                                     | 19 |

|      | Commande de l'allumage d'une DEL.                                 | 19 |

| 1.28 | Afficheur 7 segements                                             | 20 |

|      | Afficheur 7 segements à anode commune                             | 20 |

|      | Afficheur 7 segements à anode commune                             | 21 |

| 2.1  | Schéma Electrique du testeur de temps de réaction                 | 23 |

| 2.2  | le schéma de câblage du NE555                                     | 25 |

| 2.3  | Signal de sortie du NE555 - BP1 relâché                           | 26 |

| 2.4  | Signal de sortie du NE555 - BP1 actionné                          | 27 |

| 2.5  | La Division de fréquence                                          | 28 |

| 2.6  | Le Signal obtenu à la sortie du CD4040 - BP1 relâché              | 29 |

| 2.7  | Le Signal obtenu à la sortie du CD4040 - BP1 actionné                       | 30 |

|------|-----------------------------------------------------------------------------|----|

| 2.8  | Le Générateur d'impulsions                                                  | 30 |

| 2.9  | Le signal de sortie du générateur d'impulsions sans la diode                | 31 |

| 2.10 | Le signal de sortie du générateur d'impulsions après la diode - BP1         |    |

|      | relâché                                                                     | 32 |

| 2.11 | Le signal de sortie du générateur d'impulsions après la diode-Boutton       |    |

|      | poussoir actionnéé                                                          | 32 |

| 2.12 | la partie qui réalise la fonction hasard                                    | 33 |

|      | la partie qui réalise la fonction hasard                                    | 34 |

|      | le signal prélevé au niveau de la diode                                     | 34 |

|      | Le Circuit Intégré CD 4060                                                  | 35 |

|      | Le signal de sortie lorsque BP1 et BP2 sont relâchés                        | 36 |

|      | Le Rapport cyclique d'un signal carré.                                      | 36 |

|      | chronométrage du temps de réaction                                          | 37 |

|      | L'affichage lors de l'initialisation                                        | 38 |

|      | Premier résultat de test sur simulation                                     | 38 |

|      | Deuxième résultat de test sur simulation                                    | 39 |

|      |                                                                             |    |

| 3.1  | Présentation du circuit finale.                                             | 40 |

| 3.2  | Le Signal à la sortie du NE555 lorsque le bouton BP1 est reâché             | 41 |

| 3.3  | Le Signal à la sortie du NE555 lorsque le bouton BP1 est Appuyé             | 41 |

| 3.4  | Le Signal à la sortie du CD4040 lorsque le bouton poussoir est relâché.     | 42 |

| 3.5  | Le Signal à la sortie du CD4040 lorsque le bouton poussoir est actionné.    | 42 |

| 3.6  | Le Signal à la sortie du dérivateur lorsque le bouton poussoir est relâché. | 43 |

| 3.7  | La mise sous tension du testeur de temps de réaction                        | 46 |

| 3.8  | Allumage de la DEL par action sur les deux boutons poussoirs BP1            |    |

|      | et BP2.                                                                     | 47 |

| 3.9  | Test de de temps de réaction sur Mr. BRIXI NIGASSA Med El Amine.            | 47 |

| 3.10 | Test de temps de réaction sur Mr. Taberkit Med Amine                        | 48 |

|      | Réponse du troisième sujet test après 10 secondes                           | 48 |

|      | Réponse du dernier sujet test après 99 secondes                             | 49 |

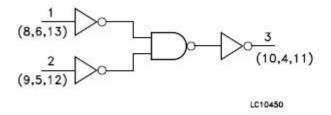

| 1    | Brochage du CD 4001                                                         | 54 |

| 2    | Diagramme logique du CD4001                                                 | 55 |

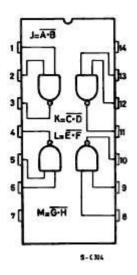

| 3    | Brochage du CD 4011                                                         | 56 |

| 4    | Diagramme logique du CD4011                                                 | 57 |

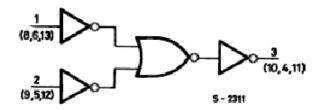

| 5    | Brochage du CD 4060                                                         | 58 |

| 6    | Diagramme Fonctionnel du CD 4060                                            | 59 |

| 7    | Détails sur la partie compteur binaire du CD 4060                           | 59 |

| 8    | Détails sur la partie oscillateur du CD 4060                                | 60 |

| 9    | Oscillateur à Quartz                                                        | 60 |

| 10   | Brochage du CD 4511                                                         | 61 |

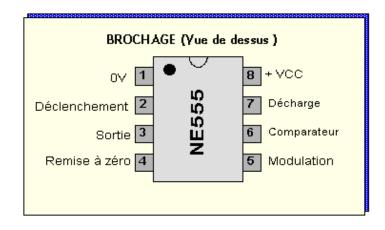

| 11   | Brochage du NE555                                                           | 63 |

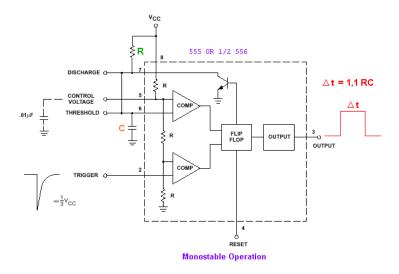

| 12   | Montage de fonctionnement monostable du NE555                               | 65 |

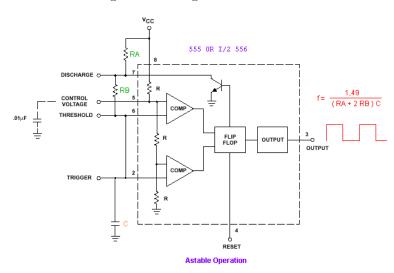

| 13   | Montage de fonctionnement astable du NE555                                  | 65 |

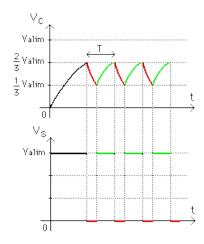

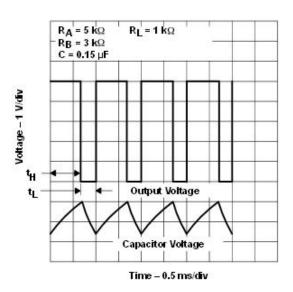

| 14   | Diagramme temporel en fonctionnement astable                                | 66 |

| 15   | Forme Typique d'onde en Astable                                             | 66 |

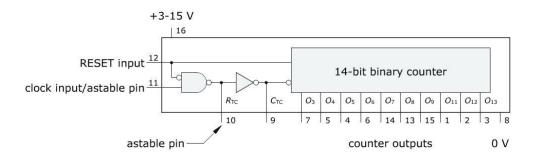

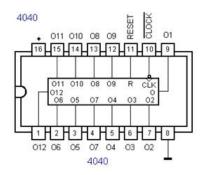

| 16   | Brochage du CD4040                                                          | 68 |

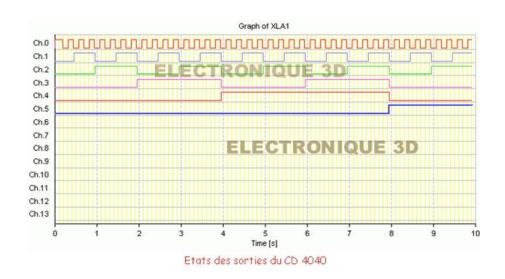

|      | États des sorties du CD4040                                                 |    |

TABLE DES FIGURES VIII

| 18 | Brochage du CD4518 71                    |

|----|------------------------------------------|

| 19 | Table de Vérité du CD4518                |

| 20 | Chronogramme du Double compteur BCD 4518 |

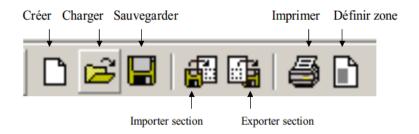

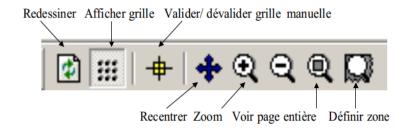

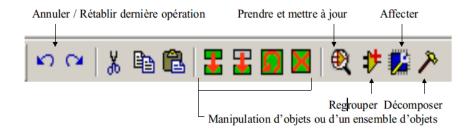

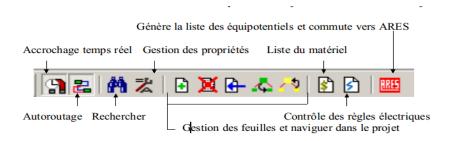

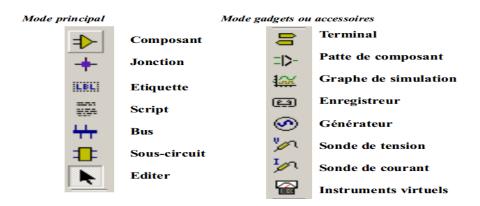

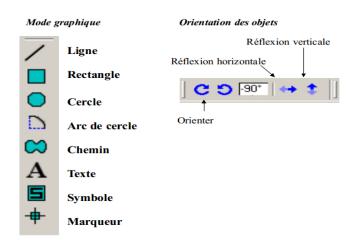

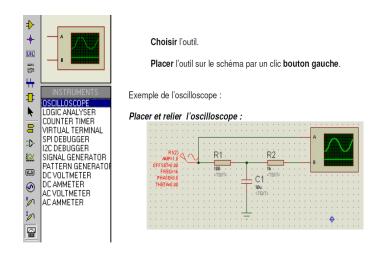

| 21 | Menu Commandes                           |

| 22 | Menu Commandes                           |

| 23 | Menu Commandes                           |

| 24 | Menu Commandes                           |

| 25 | Menu Commandes                           |

| 26 | Menu Commandes                           |

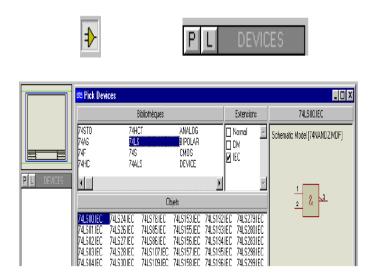

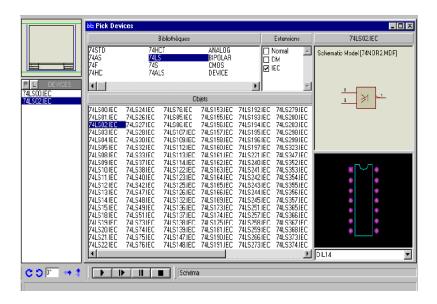

| 27 | Recherche des composants                 |

| 28 | Selection des composants                 |

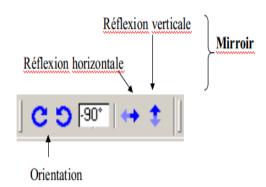

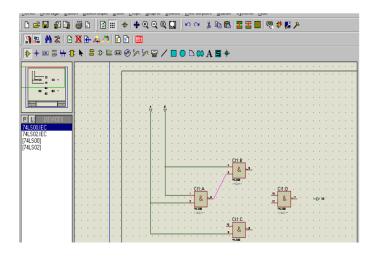

| 29 | Placement des composants 79              |

| 30 | Réalisation des liasons entre composants |

| 31 | L'Ajout des générateurs                  |

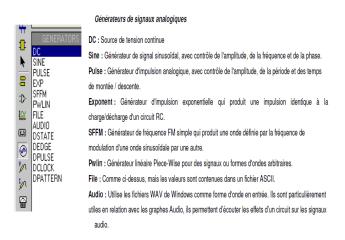

| 32 | Les outils interactifs                   |

| 33 | Lancement de L'Animation                 |

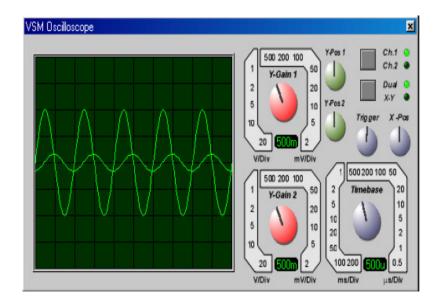

| 34 | L'Affichage dans L'oscilloscope          |

| 35 | Netlist Transfert to ARES                |

TABLE DES FIGURES İX

## Liste des tableaux

| 1.1  | Table de vérité de l'inverseur                                   | 6  |

|------|------------------------------------------------------------------|----|

| 1.2  | Table de vérité de la porte AND                                  | 7  |

| 1.3  | Table de vérité de la porte NAND                                 | 7  |

| 1.4  | Table de vérité de la porte OR                                   | 8  |

| 1.5  | Table de vérité de la porte NOR                                  | 8  |

| 1.6  | Table de vérité de la porte XOR                                  | 9  |

| 1.7  | Table de vérité de la porte NXOR                                 | 9  |

| 1.8  | Table de vérité de la Bascule RS                                 | 11 |

| 1.9  | Table de vérité de La Bascule JK                                 | 13 |

| 1.10 | Table de vérité des compteurs asynchrones                        | 16 |

| 2.1  | Tableau de fréquences                                            | 28 |

| 2.2  | La Table de vérité                                               |    |

| 1    | Description des Pins du CD 4001.                                 | 54 |

| 3    | Les états d'entrée et de sortie du CD 4001.                      |    |

| 2    | Conditions de fonctionnement recommandées par le constructeur du |    |

|      | CD 4001                                                          | 55 |

| 4    | Description des Pins du CD 4011.                                 | 56 |

| 6    | Les états d'entrée et de sortie du CD 4011.                      |    |

| 5    | Conditions de fonctionnement recommandées du CD 4011             | 57 |

| 7    | Description des Pins du CD 4060.                                 | 58 |

| 8    | Description des Pins du CD 4511.                                 | 61 |

| 9    | Conditions de fonctionnement recommandées du CD 4511             | 62 |

| 10   | Table de vérité du CD 4511                                       | 62 |

| 11   | Désignation des broches du NE555                                 | 64 |

| 12   | Désignation des broches du CD4040                                | 69 |

| 13   | Désignation des broches du CD4518                                | 71 |

#### Introduction

Dans un monde ou les accidents de la route prennent de plus en plus des proportions alarmantes, des efforts considérables sont mis en œuvres par différents acteurs tels que les constructeurs automobiles qui développent des systèmes de plus en plus intelligents destinés à l'aide aux automobilistes dans les situations d'urgences, la gendarmerie nationale, la police afin de limiter ces derniers, Mais un facteur reste toujours en suspens et qui est l'une des causes majeur d'accidents de la route, c'est le temps de réaction. Le temps de réaction correspond à la durée séparant une stimulation donnée d'une réponse. Ce dernier est très souvent improprement appelé « Réflexes » ce qui est complètement faux car le réflexe est une action involontaire alors que le temps de réaction est une action volontaire.

L'importance de ce temps de réaction est absolument primordiale, car il va nous permettre de nous renseigner sur l'état de fatigue du sujet testé. Ce facteur peut prendre des proportions considérables suite à la consommation d'alcool ou produits stupéfiants ou même encore certains médicaments.

Dans le cadre de notre projet de fin d'étude, nous proposons un montage permettant de mesurer ce temps de réaction avec une certaine précision.

Ce Travail a fait l'objet de 3 chapitres :

Le premier chapitre consacré à la présentation du projet. Dans ce chapitre on a donnés alors le schéma synoptique de notre réalisation.

Le second chapitre permettra de détailler chacun des blocs constituants notre système.

Le dernier chapitre sera consacré à la présentation des différents résultats obtenus.

## Chapitre 1

# Schéma synoptique et étude théorique

Dans ce chapitre seront présentées quelques généralités sur les différents composants de base constituants notre circuit testeur de temps de réaction, ce qui va servir par la suite à la bonne compréhension du principe de fonctionnement de ce dernier. Nous allons dans un premier temps donner le schéma bloc de notre circuit, en définissant le rôle de chaque partie et en introduisant par la suite des notions sur les principaux circuits électroniques de base constituant chaque partie de notre système.

#### 1 Schéma fonctionnel du testeur de temps de réaction

Le schéma synoptique du testeur de temps de réaction réalisé est présenté sur la figure 1.1.

il se compose:

- d'une partie génération de la base de temps.

- d'un Trigger.

- d'une partie d'affichage.

FIGURE 1.1 – Schéma fonctionnel du testeur de temps de réaction.

La première étape de notre réalisation consiste à générer un train d'impulsions. Ce signal servira de signal d'horloge pour les circuits constituants notre réalisation d'où la nécessité d'expliquer comment générer ce signal.

#### 2 Les Circuits multivibrateurs astables

Un circuit astable est un générateur autonome délivrant un signal rectangulaire périodique. Plusieurs structures électroniques existent, parmi les plus utilisées on a [1] [3]:

- Montage astable à circuit intégré NE555.

- Montages astables à base d'amplificateur opérationnel.

- Montage astable à portes logiques.

Pour le circuit intégré NE555, tout est expliqué dans la partie annexes.

#### 2.1 Montages astables à base d'amplificateur opérationnel

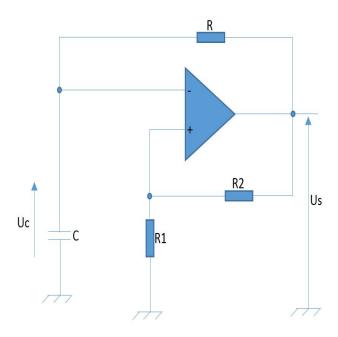

FIGURE 1.2 – Montages astables à base d'amplificateur opérationnel.

Il est composé d'un comparateur a Hystérésis qui va comparer deux seuils, commandé par un circuit RC.

On calcule ses seuils de basculement comme pour un comparateur à deux seuils. [1] [3]

$$U_{B}^{+} = U_{SAT}^{+} \cdot \frac{R}{R_{1} + R_{2}}$$

$$U_{B}^{-} = U_{SAT}^{-} \cdot \frac{R}{R_{1} + R_{2}}$$

FIGURE 1.3 – La charge et la décharge du condensateur du ontage astable à base d'AOP.

On se rend compte à partir de cette caractéristique que la période du signal  $U_s$  est définie par la durée de charge et de décharge du condensateur (tension Uc). Entre t1 et t2 le condensateur se charge, à travers R, vers  $U_{SAT}^+$ , mais à t2 il atteint le seuil haut ce qui fait changer  $U_s$ , il se charge alors vers la tension  $U_{SAT}^-$  jusqu'à ce qu'il atteigne la valeur  $U_B^-$ .

#### Calcul de la période :

On utilise le temps de charge du condensateur pour calculer la période. Cette formule nous permet de calculer le temps que met le condensateur pour se charger d'une valeur précise à une autre.

$$t = \tau \cdot \ln\left(\frac{U_{Cmax} - U_{Ct1}}{U_{Cmax} - U_{Ct2}}\right)$$

Nous allons calculer le temps entre t1 et t2. Ici égale à R.C. Au début de ce temps la tension aux bornes du condensateur est de  $U_B^-$ , à la fin, elle vaut  $U_B^+$ :

$$t = R.C. \ln(\frac{U_{SAT}^{+} - U_{B}^{+}}{U_{SAT}^{+} - U_{B}^{-}})$$

Ici les seuils sont symétriques ( $U_{SAT}^+ = U_{SAT}^-$ ) donc le rapport cyclique (temps à l'état haut sur la période) est de 50%. On peut donc se passer de calculer le temps de décente qui est le même, et trouver le résultat en multipliant par 2.

#### 2.2 Montages à portes logiques

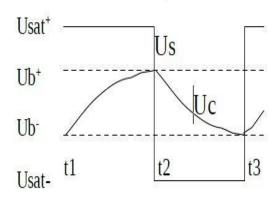

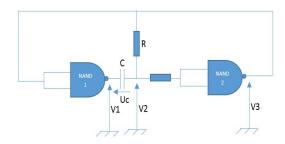

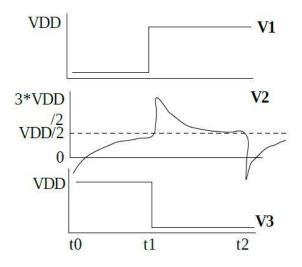

Ce montage astable fonctionne avec deux portes logiques NAND, le condensateur se charge à travers la résistance R. [1]

Figure 1.4 – Montage astable à portes logiques .

FIGURE 1.5 – La tension  $V_{DD}$  en fonction de V1, V2 et V3. [1]

A l'instant t0 : la porte NAND1 est à l'état bas, la porte NAND2 est donc à l'état haut. Le condensateur se charge, à travers la résistance R, entre la sortie de la porte NAND1 (la masse) et la sortie de la NAND2. L'entrée de NAND2, n'appelant pas de courant, est négligeable.

A l'instant t1 : la tension V1 dépasse  $\frac{V_{DD}}{2}$  (le seuil de la porte NAND). La NAND2 bascule alors à l'état bas et la NAND 1 à l'état haut. On a donc :

V1 est à VCC et la sortie de la NAND2 à la masse. Comme Uc ne peut pas varier brusquement il est encore à  $\frac{V_{DD}}{2}$ .

La tension VDD est donc égale a  $V_2 = V1 + U_c = V_{DD} + \frac{V_{DD}}{2} = \frac{3.V_{DD}}{2}$  .

A t2 : Le condensateur se charge négativement de  $\frac{3.V_{DD}}{2}$  vers 0 jusqu'à ce que  $V_1$  dépasse  $\frac{-V_{DD}}{2}$ , moment où la porte NAND2 bascule à l'état haut et la NAND1 à l'état bas, on retrouve le même schéma qu'au temps t1 :  $V_2 = V_1 + U_c = 0 + U_c = \frac{-V_{DD}}{2}$

#### 3 Les portes logiques

#### 3.1 L'inverseur

Cette porte agit sur un seul bit. Sa fonction est d'inverser tous simplement le bit d'entrée. [4]

$$S = \overline{A}$$

Son symbôle est donnée par la figure 1.6 :

FIGURE 1.6 – L'inverseur. [2]

Sa table de vérité est donnée par la table 1.1 :

| A | S |

|---|---|

| 0 | 1 |

| 1 | 0 |

Table 1.1 – Table de vérité de l'inverseur.

#### 3.2 La porte AND

Cette porte contrairement à la précédente comprend deux entrées et une seule sortie. Dans ce cas on effectue une fonction ET logique entre les deux entrées.

$$S = A.B$$

Son symbôle est donné par la figure 1.7:

FIGURE 1.7 – La porte logique AND. [2]

Sa table de vérité est donnée par la table 1.2 :

3. Les portes logiques 6

| A | В | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Table 1.2 – Table de vérité de la porte AND.

#### 3.3 La porte NAND

Cette porte présente la particularité de pouvoir recréer des portes AND, OR, NON dans un circuit électronique en utilisant seulement des montages composés d'uniquement des portes NAND. On effectue toujours une opération ET logique entre les deux sorties mais cette fois le résultat obtenue est inversé :

$$S = \overline{A.B}$$

Son symbôle est donné par la figure 1.8 :

FIGURE 1.8 – La porte NAND. [2]

Sa table de vérité est donnée par la table 1.3 :

| A | В | S |

|---|---|---|

| 0 | 0 | 1 |

|   | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table 1.3 – Table de vérité de la porte NAND.

#### 3.4 La porte OR

La sortie S obtenue est le résultat d'un OU logique entre les deux entrées :

$$S = A + B$$

Son symbôle est donné par la figure 1.9 :

FIGURE 1.9 – La porte OR. [2]

3. Les portes logiques 7

Sa table de vérité est donnée par la table 1.4 :

| Entrée 1 | Entrée 2 | Sortie |

|----------|----------|--------|

| 0        | 0        | 0      |

| 0        | 1        | 1      |

| 1        | 0        | 1      |

| 1        | 1        | 1      |

Table 1.4 – Table de vérité de la porte OR.

#### 3.5 La porte NOR

Içi la sortie S obtenue sera le résultat inverse d'un OU logique entre les deux entrées :

$$S = \overline{A + B}$$

Son symbôle est donné par la figure 1.10 :

FIGURE 1.10 – La porte NOR. [2]

Sa table de vérité est donnée par la table 1.5 :

| Entrée 1 | Entrée 2 | Sortie |

|----------|----------|--------|

| 0        | 0        | 1      |

| 0        | 1        | 0      |

| 1        | 0        | 0      |

| 1        | 1        | 0      |

Table 1.5 – Table de vérité de la porte NOR.

#### 3.6 La porte XOR

$$S = A \oplus B$$

Son symbôle est donnée par la figure 1.11:

FIGURE 1.11 – La porte XOR. [2]

Sa table de vérité est donnée par la table 1.6 :

3. LES PORTES LOGIQUES 8

| a | b | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table 1.6 – Table de vérité de la porte XOR.

$$S = a\overline{b} + \overline{a}b$$

#### 3.7 La porte NXOR

Exécute la fonction inverse du Ou exclusif :

$$S = \overline{A \oplus B}$$

Son symbôle est donnée par la figure 1.12 :

FIGURE 1.12 – La porte NXOR. [2]

Sa table de vérité est donnée par la table 1.7 :

| a | b | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Table 1.7 – Table de vérité de la porte NXOR.

$$S = \overline{a}\overline{b} + ab$$

Remarque: Dans notre montage, on s'intéressera plus aux portes logique NAND et NOR, car c'est ces deux types de portes qui sont utilisées dans les circuits intégrés CD4001 et CD4011 dont nous avons besoin.

#### 4 Les bascules

Une bascule est un dispositif électronique susceptible de changer d'état binaire à l'arrivée d'une commande, mais elle présente aussi la particularité de conserver cet état jusqu'à l'apparition d'un autre signal de commande. Ce dispositif constitue

4. LES BASCULES 9

donc une mémoire.

Donc ce qu'il faut retenir ici c'est que le signal de sortie de la bascule dépend non seulement de la combinaison des entrées, mais aussi des états antérieurs. [1] [4]

Il existe plusieurs types de bascules, dans ce qui suit nous allons citer les bascules les plus utilisées.

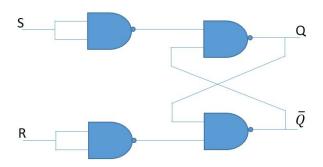

#### 4.1 Bascule RS

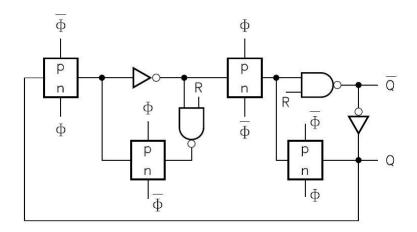

Le circuit de base d'une bascule RS est représenté en fonction de portes NAND par la figure 1.13 :

FIGURE 1.13 – La Bascule RS.

Son chronogramme est donnée par la figure 1.14 :

FIGURE 1.14 – Le chronogramme de La Bascule RS.

Donc ce qu'on peut dire à partir de la forme d'onde est que :

- La bascule est au repos dans le cas ou : R = S = 0

- La mise à 1 de la bascule (mise à 1 de Q) se fait dans le cas ou : S = 1 et R = 0 (S : SET).

4. LES BASCULES 10

- La mise à zéro de la bascule se fait dans le cas ou : S = 0 et R = 1 (R : Reset).

- Ce type de bascule présente un état dit « interdit » et ceci dans le cas ou S=R=1.

La Table de vérité donnée par la table 1.8 résume tous ce qu'on vient de dire :

| $\mathbb{R}$            | S | Q        |  |  |

|-------------------------|---|----------|--|--|

|                         | 0 | Mémoire  |  |  |

|                         | 1 | 1        |  |  |

| $\parallel 1 \parallel$ | 0 | 0        |  |  |

| $\parallel 1 \parallel$ | 1 | Interdit |  |  |

Table 1.8 – Table de vérité de la Bascule RS.

Remarque : Une application très intéressante de ce type de bascule est le circuit anti-rebonds.

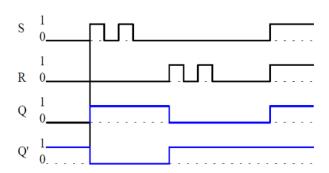

#### 4.2 Bascule RSH

L'Amélioration de la bascule RS peut se faire en rajoutant à cette dernière une entrée horloge, comme le montre la figure 1.15 :

FIGURE 1.15 – La Bascule RSH.

Le chronogramme dans ce cas devient :

4. Les bascules 11

FIGURE 1.16 – Le chronogramme de La Bascule RSH.

Ici on peut remarquer qu'à la différence de la bascule RS de base, la sortie de la bascule RSH dépend aussi du signal d'horloge.

- la bascule est bloquée et les entrées R et S sont inactives lorsque le signal d'horloge  ${\cal H}=0$

- La bascule RSH fonctionne comme la bascule RS dans le cas où le signal d'horloge H = 1 et dans ce cas on dit que la bascule est transparente.

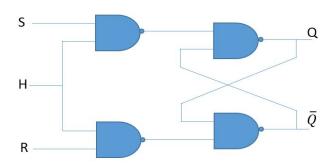

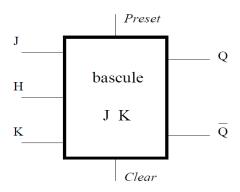

#### 4.3 Bascule JK

Cette bascule présente l'avantage de lever l'état interdit qu'on trouve dans la bascule RS. Ce type de bascule est utilisé pour faire des compteurs modulo n (2n).

FIGURE 1.17 – La Bascule JK

Le chronogramme de ce type de bascule est donné sur la figure 1.18 :

4. LES BASCULES 12

FIGURE 1.18 – Le chronogramme de La Bascule JK.

Les entrées J et K ont le même rôle que les entrées R et S de la précédente bascule mais leur effet en sortie n'a lieu qu'après la réception d'un front d'horloge.

Lorsque les deux entrées sont au niveau 1, la sortie Q change d'état à chaque front d'horloge.

<u>Remarque</u>: généralement les circuits comportent également des entrées asynchrones de mise à zéro et de mise à un, qui permettent de forcer la sortie Q respectivement aux niveaux 0 et 1.

La table de vérité de ces bascules est représentée par la table 1.9 :

| J | K | $Q_n$ | $Q_{n+1}$        | Résultat                                   |

|---|---|-------|------------------|--------------------------------------------|

| 0 | 0 | $Q_n$ | $Q_{n+1}$        | repos(mémoire)                             |

| 0 | 1 | $Q_n$ | 0                | mise à zéro de Q (Reset)                   |

| 1 | 0 | $Q_n$ | 1                | mise à un de Q (Set)                       |

| 1 | 1 | $Q_n$ | $\overline{Q_n}$ | Changement d'état à chaque front d'horloge |

Table 1.9 – Table de vérité de La Bascule JK.

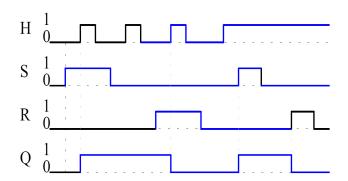

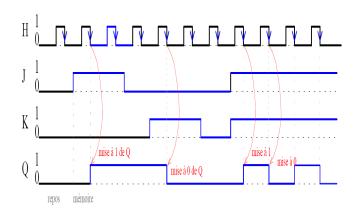

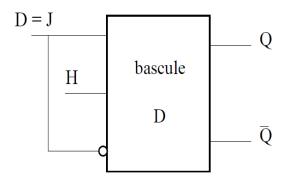

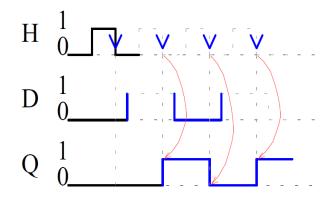

#### 4.4 Bascule D

C'est cette bascule qui nous intéresse dans notre étude. Cette bascule représente un cas particulier de la bascule JK, elle correspond à la combinaison  $D=J=\overline{K}$ .

4. LES BASCULES 13

Figure 1.19 – La Bascule D.

chronogramme de cette bascule est :

Figure 1.20 – chronogramme de La Bascule D.

#### 5 Les compteurs Binaires

Il existe deux types de compteurs binaires, les compteurs dits asynchrones et des compteurs synchrone.

en ce qui nous concerne, nous utiliserons les compteurs asynchrones que nous détaillons dans ce que suit.

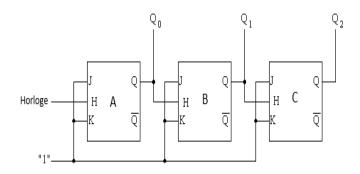

#### 5.1 Les compteurs asynchrone (Ripple Counter)

C'est un ensemble de bascules connectées de la manière suivante :

Les impulsions d'horloge sont appliquées à la borne H (Horloge) de la première bascule A, celle-ci change d'état à chaque fois qu'arrive un front déclencheur du signal d'horloge (Front montant ou front descendent).

Les entrées J et K sont mises à 1.

La sortie normale de la bascule A représente le signal d'horloge de la deuxième bascule B, cette dernière va changer d'état à chaque fois qu'arrive un front déclencheur de la bascule A.

De la même manière, la bascule C change d'état à chaque fois que la sortie B fournit un front déclencheur à celle-ci.

La figure 1.21 représente un exemple d'un compteur asynchrone modulo 8 :

FIGURE 1.21 – Compteur asynchrone modulo 8. [5]

Le chronogramme obtenu à partir de cet exemple est donné par la figure 1.22:

FIGURE 1.22 – chronogramme d'un compteur asynchrone modulo 8. [5]

Remarque : Le front déclencheur pris dans cet exemple est un front descendant.

Le tableau 1.10 suivant montre la suite des états binaires pris pour les bascules après chaque impulsion d'horloge.

| Nbre d'impulsions | $Q_2$ | $Q_1$ | $Q_0$ |

|-------------------|-------|-------|-------|

| 0                 | 0     | 0     | 0     |

| 1                 | 0     | 0     | 1     |

| 2                 | 0     | 1     | 0     |

| 3                 | 0     | 1     | 1     |

| 4                 | 1     | 0     | 0     |

| 5                 | 1     | 0     | 1     |

| 6                 | 1     | 1     | 0     |

| 7                 | 1     | 1     | 1     |

| 8                 | 0     | 0     | 0     |

| 9                 | 0     | 0     | 1     |

Table 1.10 – Table de vérité des compteurs asynchrones.

A l'arrivé de la première impulsion d'horloge, la bascule A passe à l'état haut alors que les autres bascules sont à l'état bas, on est donc sur la combinaison 001.

A l'arrivé de la deuxième impulsion, ce qui constitue un front déclencheur à l'entrée horloge de la bascule B, et donc force cette dernière à passer à l'état haut au quel correspond la combinaison 010, et ainsi de suite jusqu'à atteindre la combinaison 111 qui correspond à la septième impulsion d'horloge.

Arrivé à la huitième impulsion d'horloge, toutes les bascules reviennent à leur état initial 000, et dans ce cas on dit que le compteur est **recyclé** et qu'il recommence un nouveau cycle de dénombrement des impulsions.

#### Le modulo d'un compteur

Le compteur qu'on a vu précédemment possède 8 états distincts (de 000 à 111), on dit alors que c'est un compteur asynchrone <u>Modulo 8</u>.

Le modulo donc représente le nombre total de combinaisons successives du compteur pendant un cycle complet avant son retour à l'état initial.

Le modulo d'un compteur peut être porté à une valeur plus élevé en augmentant simplement le nombre de bascules du compteur, on a donc :

$Modulo = 2^n$

Où n ici représente le nombre de bascules du compteur.

**Exemple:** Quatre bascules nous donnent un compteur asynchrone Modulo 16 (2<sup>4</sup>), ce qui correspond à 16 états distincts (de 0000 jusqu'à 1111).

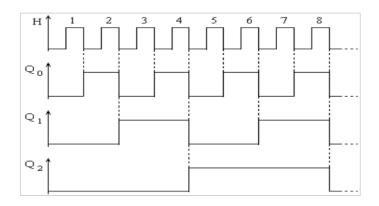

#### La division de fréquence

Reprenons l'exemple précédent du compteur asynchrone Modulo 8, on peut remarquer que la sortie de chaque bascule est une forme d'onde dont la fréquence est la moitié de la fréquence du signal d'horloge.

Considérons dans un premier temps la sortie  $Q_0$  de la première bascule A :

FIGURE 1.23 – chronogramme de la sortie Q0 du compteur asynchrone Modulo 8. [5]

Supposons que la fréquence du signal d'horloge appliquée est de 8KHz (T =  $125\mu$ s).

Le signal carré obtenu à la sortie de la bascule A a une fréquence de 4KHz car  $T_A=2T=250\mu\mathrm{s}$ .

Ce signal est appliqué maintenant à la bascule B, ce qui implique une division de fréquence par 4 à la sortie  $Q_1$ , donc f = 2KHz ( $T_B = 4T = 500 \mu s$ ).

En règle générale, la sortie de la dernière bascule d'un compteur est un signal dont la fréquence est la fréquence du signal d'horloge divisée par le modulo du compteur. Donc le signal de sortie de la bascule C aura une fréquence égale à :

$$f = \frac{8KHz}{8} = 1KHz$$

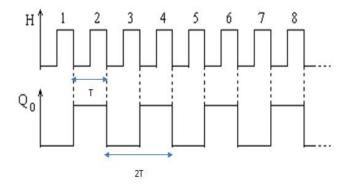

#### 5.2 Les compteurs synchrones

Ce sont des compteurs dont les différents étages sont commandés par le même signal d'horloge contrairement au compteur asynchrone.

A la différence des compteurs asynchrones, ce mode de fonctionnement autorise des vitesses de fonctionnements plus élevés du fait que la durée de la période d'instabilité est limitée [4].

#### Modèle de compteur synchrone

[6] Nous présentons brievement les compteurs synchrones que nous utiliserons pas dans notre réalisation.

Considérons le compteur modulo 4 (diviseur par 2) donné par la figure 1.24 :

FIGURE 1.24 – compteur synchrones Modulo 4.

# 6 Les diodes Électroluminescentes DEL(LED en Anglais)

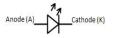

Le mot DEL est l'acronyme de Diode Electroluminescente en français (Light Emitting Diode en Anglais). Son symbôle est donné par la figure 1.25 :

FIGURE 1.25 – Symbôle d'une diode Électroluminescente DEL.

Les diodes DEL peuvent diffuser une lumière rouge, jaune ou verte et elles ont un corps de forme ronde, carrée ou rectangulaire. Ces diodes comme on l'a déjà cité auparavant s'allument seulement lorsqu'elle sont polarisées en directe c'est-à-dire que l'anode est reliée au pôle positif et la cathode au pôle négatif de l'alimentation.

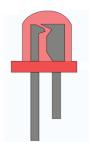

FIGURE 1.26 – Diode Électroluminescente DEL. [7]

Ce qu'il faut retenir par cœur, c'est qu'une diode DEL ne doit jamais être reliée directement à la source d'alimentation car elle serait détruite en quelques secondes. Pour commander l'allumage d'une diode DEL sans l'endommager, il faut la relier en série avec une résistance capable de réduire le courant à une valeur comprise entre 0,015 et 0,017 ampère, soit entre 15 et 17 milliampères.

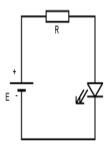

FIGURE 1.27 – Commande de l'allumage d'une DEL. [8]

Pour calculer la valeur de la résistance R, on utilise la formule suivante :

$$R = \frac{V_{cc} - V_{DEL}}{I_{moy}}$$

Où:

$V_{cc}$ : est la valeur de tension de l'alimentation.

$V_{DEL}$ : est la chute de tension à l'intérieur de la diode LED, elle est égale à 0.7V  $I_{mou}$ : est le courant moyen exprimé en ampère, sa valeur est de 16mA.

**Exemples :** Si on veut alimenter une DEL avec une pile de 4,5V, on devra relier cette dernière avec une résistance de :

$$R = \frac{4.5 - 0.7}{0.016} = 237.5\Omega$$

Même chose si on veut alimenter une DEL avec une pile de 9V, on devra relier cette dernière avec une résistance de :

$$R = \frac{9 - 0.7}{0.016} = 518.75\Omega$$

#### 7 Les afficheurs 7 segments

L'afficheur est un composant composé de 7 diodes DEL en forme de segment et disposées de façon à former un 8.

FIGURE 1.28 – Afficheur 7 segements. [2]

En alimentant ces segments avec une tension continue, on peut visualiser n'importe quel nombre de 0 à 9, c'est-à-dire : 0 - 1 - 2 - 3 - 4 - 5 - 6 - 7 - 8 - 9.

#### 7.1 Fonctionnement et types

Il y deux types d'afficheurs :

- Les afficheurs à anode commune.

- Les afficheurs à cathode commune.

Il faut savoir que l'on utilise les afficheurs 7 segments, de la même manière qu'une LED.

#### 7.2 Afficheur 7-segments à anode commune

Considérons la figure 1.29 :

FIGURE 1.29 – Afficheur 7 segements à anode commune [2]

A partir de cette figure, on peut remarquer que les anodes de l'afficheur 7-segments sont toutes reliées entre elles, d'où l'appellation d'afficheur 7-segments

à anode commune.

Pour allumer cet afficheur il faut donc relier le point A au pôle positif de l'alimentation, tandis que toute les sorties de l'afficheur (a-b-c-d-e-f-g) sont reliées au pôle négatif.

#### 7.3 Afficheur 7-segments à cathode commune

Considérons maintenant la figure ci-dessous :

FIGURE 1.30 – Afficheur 7 segements à cathode commune [2]

Dans ce cas on peut remarquer que toutes les cathodes sont reliées entre elles, d'où l'appellation d'afficheur 7-segments à cathode commune.

Pour allumer ces types d'afficheurs, il faut relier le point K au pôle négatif de l'alimentation, tandis que toutes les sorties de l'afficheur (a-b-c-d-e-f-g) sont reliées au pôle positif.

Remarque : c'est de ce type d'afficheur dont on aura besoin pour la réalisation de notre testeur de temps de réaction.

#### 7.4 Calcul des résistances en sortie de l'afficheur 7-segments

L'afficheur 7-segments est composé de sept diodes DEL, donc pour calculer les résistances à insérer en sortie il faut juste reprendre la relation de calcul des résistances des diodes DEL qui est :

$$R = \frac{V_{cc} - V_{DEL}}{I_{moy}}$$

Reprenons les deux figures précédentes, on a une tension Vcc de 4,5V, donc la valeur de la résistance à insérer est :

$$R = \frac{4.5 - 0.7}{0.016} = 237.5\Omega$$

La valeur normalisée prise est donc 330  $\Omega$ .

#### 8 Conclusion

Nous avons vu dans ce chapitre les différents composants de base pouvant être introduit pour la réalisation de notre système, nous avons pu voir aussi que dans certaines parties constituant notre circuit, un choix important doit être fait quant au type de circuit à choisir pour notre application, maintenant il nous reste à bien faire ce choix et proposer un circuit simple, pratique et autonome pouvant mesurer le temps de réaction humain.

8. CONCLUSION 22

## Chapitre 2

# Présentation, Etude et simulation du système

Dans ce chapitre, le but sera de présenter le schéma électrique de notre testeur de temps de réaction, de faire l'étude électrique de ce dernier, et enfin donner quelques résultats obtenus par simulation. Pour parvenir à ça, on commencera par décomposer notre circuit en plusieurs étages, on fera une étude électrique détaillée de chaque étage en donnant les différents signaux de sorties obtenus grâce à l'outil de simulation Proteus ISIS que nous présentons en détails dans la partie Annexes. Les résultats de simulation obtenus ainsi que leurs interprétations seront présentés à la fin de ce chapitre, ainsi on pourra avoir une idée bien précise sur le bon fonctionnement de notre système avant de le réaliser sur circuit imprimé.

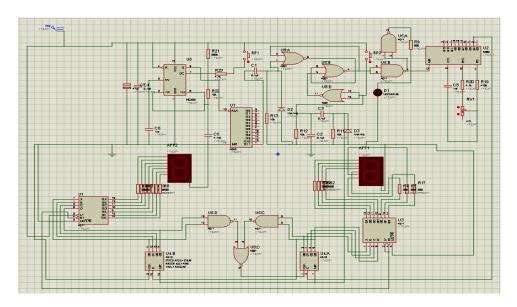

# 1 Schéma Electrique du testeur de temps de réaction

Le schéma électrique du testeur de temps de réaction que nous proposons est :

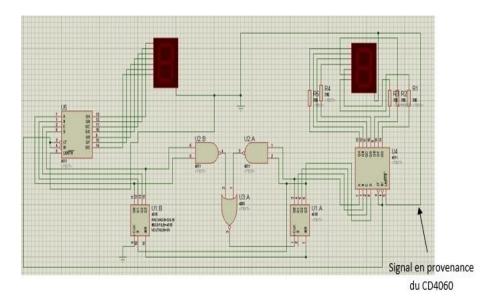

FIGURE 2.1 – Schéma Electrique du testeur de temps de réaction.

Nous allons maintenant étudier chaque étage de ce circuit et représenter les différents signaux à chaque sortie d'un étage.

### 2 Etude électrique du montage du testeur de temps de réaction

Le but de ce testeur de temps de réaction est de compter et d'afficher sur un afficheur 7-segments le temps que met le sujet test pour relâcher le bouton poussoir à l'allumage d'une LED.

Dans tout ce qui suit on a utilisé le logiciel de simulation PROTEUS pour faire la simulation de notre système.

Proteus est une suite logicielle destinée à l'électronique. Développé par la société Labcenter Electronics, les logiciels incluent dans Proteus permettent la CAO dans le domaine électronique. Deux logiciels principaux composent cette suite logicielle : ISIS, ARES, PROSPICE et VSM.

#### 2.1 Présentation générale du Logiciel Proteus

Cette suite logicielle est très connue dans le domaine de l'électronique. De nombreuses entreprises et organismes de formation (incluant lycée et université) utilisent cette suite logicielle. Outre la popularité de l'outil, Proteus possède d'autres avantages [9]

- Pack contenant des logiciels facile et rapide à comprendre et utiliser.

- Le support technique est performant.

- L'outil de création de prototype virtuel permet de réduire les coûts matériel et logiciel lors de la conception d'un projet.

#### **ISIS**

Le logiciel ISIS de Proteus est principalement connu pour éditer des schémas électriques. Par ailleurs, ce logiciel permet également de simuler ces schémas ce qui permet de déceler certaines erreurs dès l'étape de conception. Indirectement, les circuits électriques conçus grâce à ce logiciel peuvent être utilisé dans des documentations car le logiciel permet de contrôler la majorité de l'aspect graphique des circuits.

#### ARES

Le logiciel ARES est un outil d'édition et de routage qui complètement parfaitement ISIS. Un schéma électrique réalisé sur ISIS peut alors être importé facilement sur ARES pour réaliser le circuit imprimé. Bien que l'édition de ce dernier soit plus efficiente lorsqu'elle est réalisée manuellement, ce logiciel permet de placer automatiquement les composants et de réaliser le routage automatiquement.

Nous allons dans un premier temps commencer par l'étude de la partie génération de base de temps.

#### 3 Le générateur de base de temps

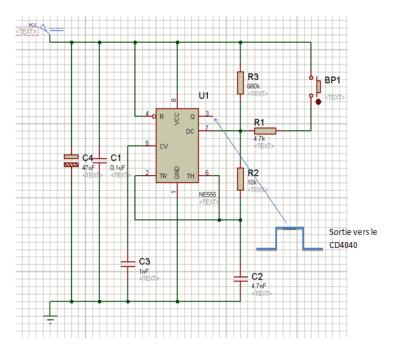

Le générateur est conçu à base du circuit intégré NE555 en montage astable. le but est de générer deux bases de temps de fréquences différentes par l'activation ou non du premier bouton poussoir BP1. Le schéma de câblage du NE555 est donné par la figure 2.2 : [10]

FIGURE 2.2 – le schéma de câblage du NE555.

les deux fréquences citées auparavant sont :

$f_1 = 440.52 \text{ Hz} \Rightarrow \text{dans le cas où le bouton poussoir BP1 est relâché.}$

$f_2 = 12.3 \text{ KHz} \Rightarrow \text{dans le cas où le bouton poussoir BP1 est actionné.}$

Maintenant on va voir comment ont été calculées ces fréquences en fonction de l'état du bouton poussoir BP1 (actionné ou relâché).

La fréquence  $f_1$  est calculée comme suite :

$$T_{H1} = 0.693(R_3 + R_2).C_2 - 9 = 0.693[(680 + 10).10^3].4.7.10^{-9} = 2.24 \text{ ms}$$

$$T_{L1}=0.693.R_2.C_2=0.693.10.10^3.4.7.10^{-9}=32.57 \ \mu s$$

$$T_1 = T_{H1} + T_{L1} = (2.24.10^{-3}) + (32.57.10^{-6}) = 2.27 \text{ ms}$$

La fréquence est donc :

$$f_1 = \frac{1}{T_1} = \frac{1}{(2.27.10^{-3})} = 440.52Hz$$

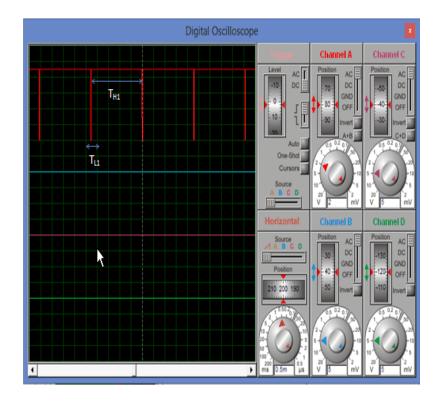

Cette fréquence correspond au cas où le bouton poussoir BP1 est relâché. Le signal obtenu par simulation est donné par la figure 2.3 :

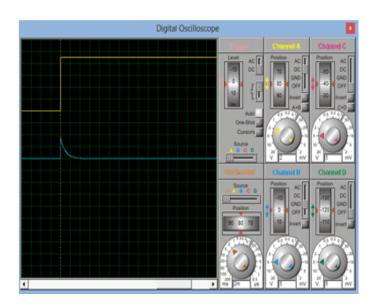

FIGURE 2.3 – Signal de sortie du NE555 - BP1 relâché

La fréquence  $f_2$  est calculée comme suite :

Dans ce cas, le bouton poussoir BP1 est actionné, et donc la résistance R1 intervient dans le calcul de cette fréquence.

La valeur de cette résistance peut être à partir de la relation suivante :

$$f = \frac{1.44}{\left[\left(\frac{R_1.R_3}{R_1+R_3}\right) + 2.R_2\right].C_2} = 12.3KHz.$$

Or  $R_3 \gg R_1$  donc la relation devient :

$$f = \frac{1.44}{(R_1 + 2.R_2).C_2} = 12300Hz$$

$$R_1 = \frac{(\frac{1.44}{12300} - 2.R_2).C_2}{C_2} = 4.9k\Omega$$

Donc la valeur normalisée  $R_1 = 4.7 \text{ k}\Omega$  sera retenue.

$$T_{H2} = 0.693.\left[\frac{R_1.R_3}{R_1.R_3} + R_2\right].C_2$$

$$T_{H2} = 0.693.\left[\left(\frac{4.7.680}{4.7+680}.10^3\right) + 10.10^3\right].4.7.10^{-9}$$

$$T_{H2} = 47.77 \ \mu s$$

$$T_{L2} = 0.693.R_2.C_2 = 0.693.10.10^3.4.7.10^{-9} = 32.57 \ \mu s$$

$$T_2 = T_H + T_L = (47.77.10^{-6}) + (32.57.10^{-6}) = 80.34 \ \mu s$$

La fréquence est donc :

$$f_2 = \frac{1}{T_2} = \frac{1}{(80.34.10^{-6})} = 12.44KHz$$

Cette fréquence correspond au cas où le bouton poussoir BP1 est actionné.

Le signal obtenu par simulation est donné par la figure 2.4 :

FIGURE 2.4 – Signal de sortie du NE555 - BP1 actionné.

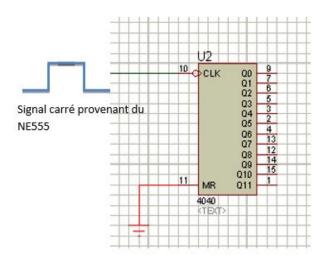

### 4 Le diviseur de fréquence

Ayant généré nos deux fréquences, on passe maintenant à la partie division de fréquence. Cette opération sera prise en charge par le circuit intégré CD4040 qui en

plus de posseder 14 étages binaire est très simple à brancher.

le but ici est de diviser les deux fréquences obtenues à partir du NE555 afin d'obtenir une temporisation de 9,5s et cela quand le bouton poussoir BP1 est relâché.

FIGURE 2.5 – La Division de fréquence.

Ce qu'on doit faire maintenant, c'est identifier la sortie qui peut nous donner une temporisation de 9,5s, pour cela on se réfère au tableau suivant :

| Sortie   | Broche | Fréquence(Hz) | Période(s) |

|----------|--------|---------------|------------|

| $Q_0$    | 9      | 5             | 0.2        |

| $Q_1$    | 7      | 2.5           | 0.4        |

| $Q_2$    | 6      | 1.25          | 0.8        |

| $Q_3$    | 5      | 0.625         | 1.6        |

| $Q_4$    | 3      | 0.3125        | 3.2        |

| $Q_5$    | 2      | 0.15625       | 6.4        |

| $Q_6$    | 4      | 0.078125      | 12.8       |

| $Q_7$    | 13     | 0.0390625     | 25.6       |

| $Q_8$    | 12     | 0.0195313     | 51.2       |

| $Q_9$    | 14     | 0.0097656     | 102.4      |

| $Q_{10}$ | 15     | 0.0048828     | 204.8      |

| $Q_{11}$ | 1      | 0.0024414     | 409.6      |

Table 2.1 – Tableau de fréquences.

Donc la sortie ici qui nous permet d'avoir cette temporisation est la sortie  $Q_{11}$  (Broche 1).

Dans le cas où le bouton poussoir est relâché :  $f_1 = 440.52 Hz$

La sortie  $Q_{11}$  correspond à une division de fréquence par 4096 ( $2^{12}$ =4096).

Donc:

A la sortie  $Q_{11}$  du CD4040, avec un bouton poussoir BP1 relâché, on obtient un signal de fréquence :

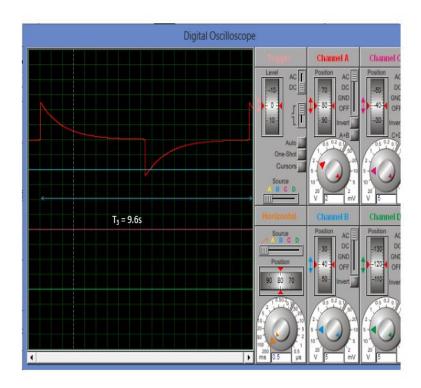

$$f_3 = \frac{440.52}{4096} = 0.1Hz$$

La période devient donc :

$$T_3 = \frac{1}{0.1} = 10s$$

Le signal obtenu en sortie est donné par la figure 2.6 :

FIGURE 2.6 – Le Signal obtenu à la sortie du CD4040 - BP1 relâché.

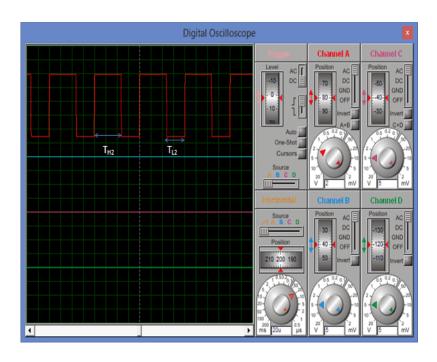

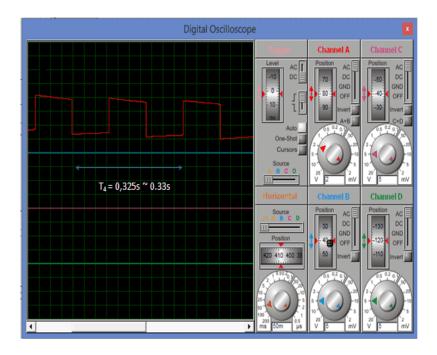

Dans le cas où le bouton poussoir est actionnée on a :

$f_2 = 12.44KHz$  quand le bouton BP1 est actionné.

A la sortie  $Q_{11}$  du CD4040, avec un bouton poussoir BP1 actionné, on obtient un signal de fréquence :

$$f_4 = \frac{12440}{4096} = 3.03Hz$$

La période devient donc :

$$T_4 = \frac{1}{3.03} = 0.33s$$

Le signal obtenu par simulation est donné par la figure 2.7 :

FIGURE 2.7 – Le Signal obtenu à la sortie du CD4040 - BP1 actionné.

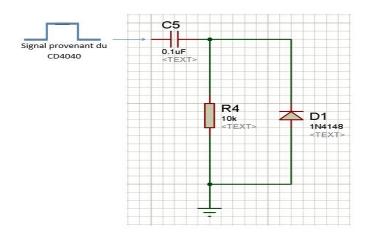

## 5 Le générateur d'impulsion en sortie du CD4040

Figure 2.8 – Le Générateur d'impulsions.

Le rôle joué ici par le circuit est un rôle de générateur d'impulsions, car dans ce cas le signal carré provenant du CD4040 va être transformé en en impulsions en gardant toujours la même période du signal en provenance du CD4040.

FIGURE 2.9 – Le signal de sortie du générateur d'impulsions sans la diode.

Dans le cas où le bouton poussoir BP1 est relâché, le signal obtenu est :

A l'instant t=0, on a :

$$V_c(t)=0$$

$$V_s(t) = V_e(t) - V_c(t)$$

Donc:

$$V_s(t) = V_e(t) = 5V$$

A l'instant  $t=t_1$ , on a :

$$V_s(t) = -V_e(t) = -5V$$

La diode dans ce cas va supprimer les impulsions négatives, car quand elle est passante, on sait que  $V_d=0.7\mathrm{V}$  et comme  $V_s(t)=-V_d$ , on récupère le potentiel négatif -0.7V comme le montre la figure 2.10 :

FIGURE 2.10 – Le signal de sortie du générateur d'impulsions après la diode - BP1 relâché.

Il ne faut pas oublier dans ce cas que la période ne change pas par rapport au signal qui est à peut-prêt égale à 9.5s.

Maintenant dans le cas où le bouton poussoir est actionné les tensions calculées auparavant ne changent pas, et la période est de 0.3 secondes, comme le montre la figure ci-dessous :

FIGURE 2.11 – Le signal de sortie du générateur d'impulsions après la diode-Boutton poussoir actionnéé.

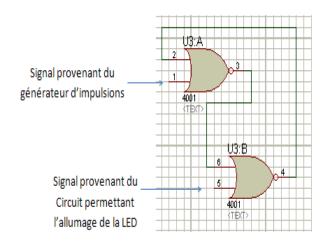

Nous allons maintenant relier ce générateur d'impulsion avec une bascule RS qui nous permettra de générer la fonction hasard, c'est à dire qu'elle va permettre l'allumage de façon à ce que l'utilisateur ne sache pas quand la LED va s'allumer.

Figure 2.12 – la partie qui réalise la fonction hasard.

#### Table de vérité

| S(Broche 5) | R (broche 1) | $Q_{n-1}$ | Q (broche3) |

|-------------|--------------|-----------|-------------|

| 0           | 0            | 0         | 0           |

| 0           | 0            | 1         | 1           |

| 0           | 1            | 0         | 0           |

| 0           | 1            | 1         | 0           |

| 1           | 0            | 0         | 1           |

| 1           | 0            | 1         | 1           |

| 1           | 1            | 0         | $\phi$      |

| 1           | 1            | 1         | $\phi$      |

Table 2.2 – La Table de vérité.

Cette bascule RS est attaqué ensuite par un signal provenant d'un circuit de restauration relié à une porte logique IV, comme le montre le schéma suivant :

Figure 2.13 – la partie qui réalise la fonction hasard.

Ici la diode va nous limiter notre tension à -0,7V, car elle polarisée en inverse. Afin d'injecter ce signal dans la porte NOR U3 :D, cette tension négative va être restaurée (on lui rajoute une composante continue), comme ça la tension injectée au niveau de la porte deviendra positive et la porte NOR U3 :D pourra ainsi fonctionner.

Le signal prélevé au niveau de la diode D2 ainsi qu'au niveau de l'entrée de la porte NOR U3 :D est :

FIGURE 2.14 – le signal prélevé au niveau de la diode.

N'oublions pas aussi que la tension prélevée aux bornes de la diode D2 va aussi servir d'entrée pour les broches '7'et '15" du double compteur BCD, le circuit intégré CD4518, ce qui permettra de déclencher la remise à zéro des afficheurs 7 segments. Maintenant le signal de sortie de la bascule RS va être injecté dans le circuit intégré

U4 qui est le circuit intégré CD4011.

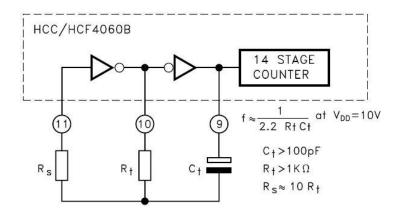

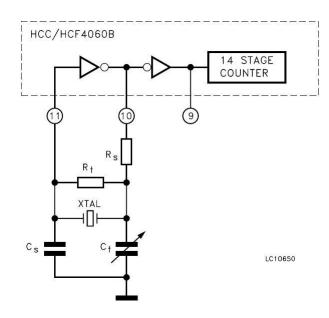

En utilisant les deux portes logiques U4A et U4B de ce circuit, on pourra amplifier le signal qui sera injecté dans la LED afin de permettre l'allumage de cette dernière. La sortie de la porte logique NAND U4B, va être injectée au circuit U5, qui est le compteur binaire quatorze étage plus oscillateur le CD4060.

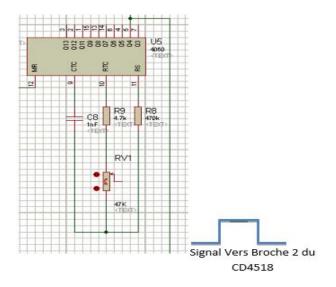

Le circuit intégré CD4060 relié en série avec les circuits précédents va nous permettre d'avoir à sa sortie un signal carré avec une période  $T = 100 \,\mathrm{ms}$ .

Il présente l'avantage de posséder un oscillateur intégré précédent le compteur binaire 14-étages.

FIGURE 2.15 – Le Circuit Intégré CD 4060.

Le calcul de la fréquence d'oscillation est donné par la relation :

$$f1 = \frac{1}{2.3 R_0 C_s} = \frac{1}{2.3 (4.7 + 47) \cdot 10^3 \cdot 10^{-9}} = 8.40 Khz.$$

$f1 = \frac{1}{2 \cdot 3 \cdot R_9 \cdot C_8} = \frac{1}{2 \cdot 3 \cdot (4 \cdot 7 + 47) \cdot 10^3 \cdot 10^{-9}} = 8.40 Khz$ . Puisque l'on prélève notre sortie à partir de la broche 5, la division de fréquence se fera par  $2^5 = 32$ .

Donc on obtient un signal de sortie avec une fréquence :

$$f = \frac{f}{32} = 262.5Hz.$$

Et donc la période T est :

$$T = \frac{1}{f} = 3.80ms.$$

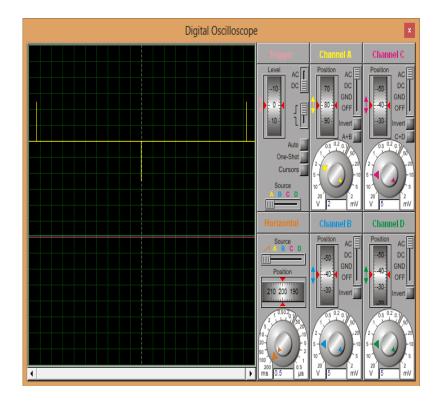

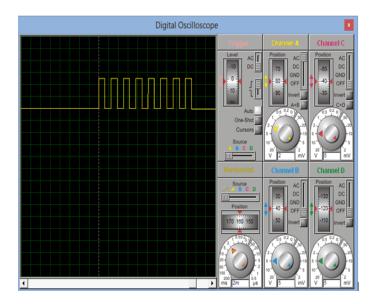

Le signal obtenu en simulation, dans le cas où les boutons poussoirs BP1 et BP2 sont relâchés donné par la figure 2.16 :

FIGURE 2.16 – Le signal de sortie lorsque BP1 et BP2 sont relâchés .

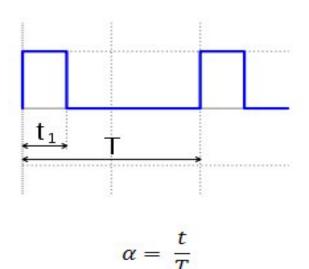

Il faut noter ici que le rôle de la résistance variable RV1 est un rôle important, car c'est grâce à cette résistance qu'on pourra faire varier le rapprot cyclique du signal carré obtenu en sortie.

Il faut rappeler que le rapport cyclique d'un signal carré est défini comme étant le rapport entre t1 et T.

FIGURE 2.17 – Le Rapport cyclique d'un signal carré.

L'intérêt ici d'utiliser un circuit RC et non pas un circuit à quartz, est que le quartz donne un rapport cyclique de 50% fixe, or on peut avoir besoin de modifier ce rapport cyclique, et pour cela nous avons placé une résistance variable RV1 en série avec la résistance R9 afin d'avoir un contrôle sur ce rapport cyclique.

La résistance R8 selon le datasheet du constructeur doit être de deux fois la résistance branché sur la broche 10 du CD4060 jusqu'à 10 fois cette même résistance

[2(R9 + RV1) < R8 < 10(R9 + RV1)].Donc on va prendre la valeur normalisé 470 k $\Omega$ .

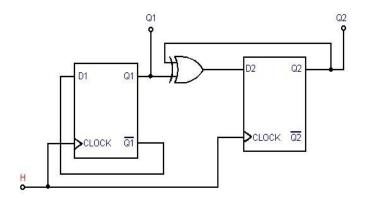

### 6 Chronométrage du temps de réflexe :

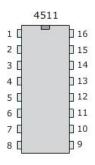

Cette opération sera réalisée à l'aide du double compteur BCD CD4518, suivi d'un décodeur BCD 7-segments.

Le signal sortant de la broche 5 du CD4060 est directement injecté dans la broche 2 du CD4518,ceci permettra la mise en marche du double compteur BCD, ainsi le CD4518 génèrera un code BCD qui sera envoyé aux deux circuits intégrés CD4511 qui sont des décodeurs BCD 7-segments et ces dernier se chargeront de décoder ces codes et d'afficher la valeur décimal de ces derniers sur un afficheur 7 segments à cathode commune.

Le schéma suivant illustre le branchement du circuit de chronométrage du temps de réaction :

FIGURE 2.18 – chronométrage du temps de réaction.

Dans ce cas bien précis, on devra introduire un système permettant de bloquer le comptage arrivé à la valeur "99", c'est le rôle joué par les deux portes NAND U2B et U2A du circuit intégré CD4011, ainsi que la porte logique NOR U3A du circuit intégré CD4001.

Arrivé à la valeur "99" qui correspond aux codes "1001 1001" on aura la sortie de la porte NAND U2A qui aura pour valeur "0", même chose pour la porte NAND U2A dont la valeur sera aussi "0". Ces deux sorties injectées dans la porte NOR U3A donneront un "1" à sa sortie ce qui va bloquer le comptage du CD 4518.

## 7 Quelques résultats obtenus en simulation

#### 7.1 L'affichage lors de l'initialisation

FIGURE 2.19 – L'affichage lors de l'initialisation.

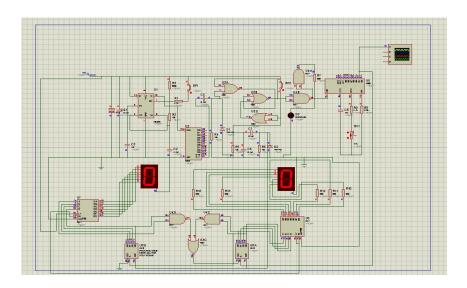

#### 7.2 Premier résultat de test sur simulation

FIGURE 2.20 – Premier résultat de test sur simulation.

Dans cet exemple le sujet test a réagi à l'allumage de la LED après deux secondes.

#### 7.3 Deuxième résultat de test sur simulation

FIGURE 2.21 – Deuxième résultat de test sur simulation.

Dans cet exemple, le sujet test a réagi après 18 secondes. Il est annoté que dans ce cas on introduit intentionnellement le retarder de réaction à l'allumage de la LED afin de voir le fonctionnement du circuit.

#### 8 Conclusion

Nous avons pu représenter dans ce chapitre les résultats de simulation obtenus aux différents nœuds de sortie de chacun des étages constituant notre testeur de temps de réaction, nous pouvons dire que ces résultats sont très prometteurs. Après avoir simulé notre testeur de temps de réaction, on présente dans le chapitre III, la réalisation pratique élaborée et nous comparons les résultats de simulation obtenus avec les résultats pratiques après les tests sur notre circuit.

8. CONCLUSION 39

## Chapitre 3

# Réalisation et résultats pratiques du testeur de temps de réaction

Dans ce chapitre, le but sera de présenter la réalisation pratique du testeur de temps de réaction, de faire l'étude et l'analyse de ce dernier, et enfin présenter les différentes résultats obtenus mais cette fois pratiquement, interpréter ces derniers et les valider en les comparant avec les résultats obtenus dans le chapitre précédent.

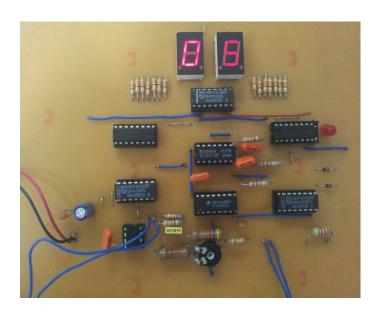

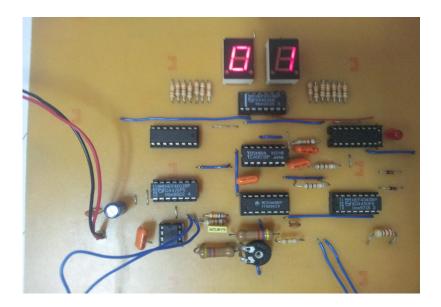

## 1 Présentation de notre circuit finale sur circuit imprimé

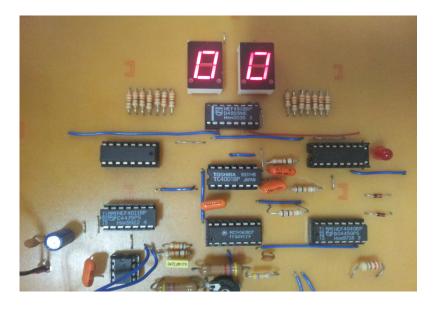

Le circuit testeur de temps de réaction que nous avons réalisé est présenté dans la figure 3.1 suivante :

FIGURE 3.1 – Présentation du circuit finale.

- 2 Prélèvement des différents signaux au niveau des noeuds de sortie de notre testeur de temps de réaction

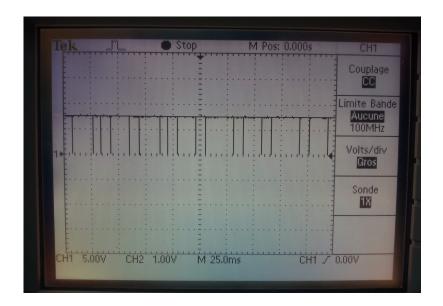

- 2.1 Signal prélevé à la sortie du circuit intégré NE555

Dans le cas où le bouton poussoir BP1 est relâché :

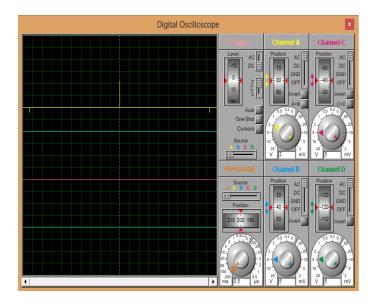

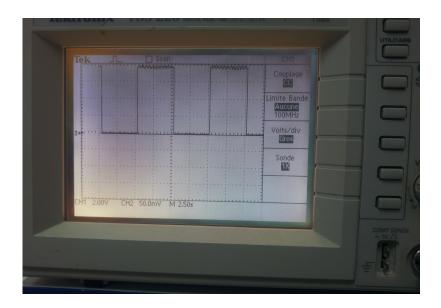

FIGURE 3.2 – Le Signal à la sortie du NE555 lorsque le bouton BP1 est reâché.

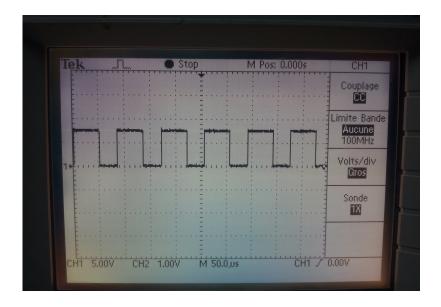

Dans le cas où le bouton poussoir BP1 est Appuyé:

FIGURE 3.3 – Le Signal à la sortie du NE555 lorsque le bouton BP1 est Appuyé.

<sup>2.</sup> PRÉLÈVEMENT DES DIFFÉRENTS SIGNAUX AU NIVEAU DES NOEUDS DE SORTIE DE NOTRE TESTEUR DE TEM $^{4}$ L DE RÉACTION

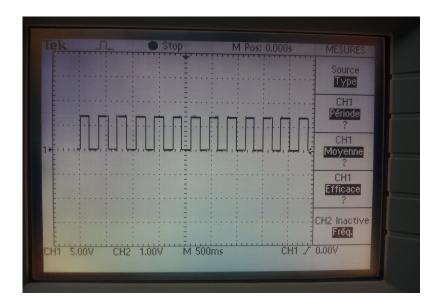

#### 2.2 Le signal à la sortie du circuit intégré CD4040

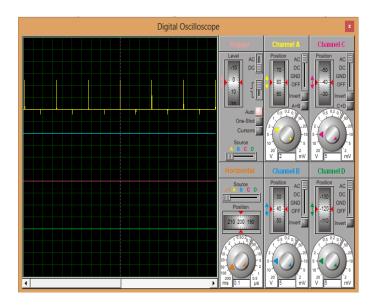

Dans le cas où le bouton poussoir est relâché :

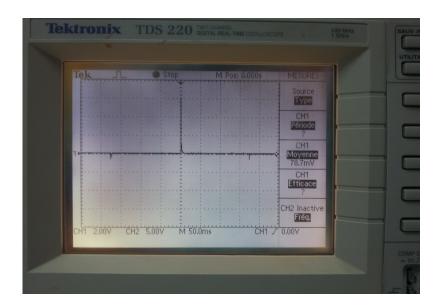

FIGURE 3.4 – Le Signal à la sortie du CD4040 lorsque le bouton poussoir est relâché.

Dans le cas où le bouton poussoir est appuyé:

FIGURE 3.5 – Le Signal à la sortie du CD4040 lorsque le bouton poussoir est actionné.

<sup>2.</sup> Prélèvement des différents signaux au niveau des noeuds de sortie de notre testeur de tem42 de réaction

#### 2.3 Le signal à la sortie du dérivateur

FIGURE 3.6 – Le Signal à la sortie du dérivateur lorsque le bouton poussoir est relâché.

#### 3 Analyse du circuit :

La capacité  $C_7$  utilisée dans le cas où nous utiliserons une alimentation secteur qui permet de délivrer un courant ondulé.

La capacité  $C_4$  fait office de capacité de découpage entre l'alimentation et le montage considéré par notre étude.

#### 3.1 Le circuit de temporisation

Le circuit intégré U6 est un NE555 qui permet de délivrer à sa sortie un signal carré. La période du signal ainsi délivré dépend des composants  $R_{23}$ ,  $R_{21}$ ,  $R_{22}$  et  $C_5$ .

Ainsi ce signal a une fréquence qui peut prendre deux valeurs selon la position du bouton poussoir BP1.

En effet si on appuie sur BP1, la période du signal délivré s'exprime par la relation :

$$T = 0.7(R_{23}//R_{21} + 2R_{22})C_5$$

Vu que  $R_{23} = 4.7 \text{k}\Omega$  et  $R_{21} = 680 \text{k}\Omega$ , alors  $R_{23}$  //  $R_{21} = R_{23}$ .

L'expression de t devient alors :

3. Analyse du circuit : 43

$$T = 0.7(R_{23} + 2R_{22})C_5 = 80\mu s$$

Donc la fréquence est :

$$f = \frac{1}{T} = \frac{1}{(80.10^{-6})} = 12,3KHz$$

Dans un second cas on BP1 n'est pas sollicité, seule  $R_{21}$  est prise en compte. La période du signal délivré a pour expression :

$$T = 0.7(R_{21} + 2R_{22})C_5 = 2.3ms$$

Donc la fréquence est :

$$f = \frac{1}{T} = \frac{1}{(2, 3.10^{-3})} = 430Hz$$

Dans les deux cas, le signal délivré par le NE555 servira de signal horloge pour le compteur référencé U1. Nous avons alors utilisé alors le compteur CD4040 qui comporte deux étages binaires montés en cascade.

Le signal carré obtenu à la sortie  $Q_{11}$  du compteur a une période  $T_{CD4040}$  telle que  $T_{CD4040}=2^{12}$  .t où t représente la période du signal délivré par le NE555.

Si BP1 est activé alors :

$$T = 4096.80 \mu s = 0.3s$$

Si BP1 n'est pas activé alors:

$$T = 4096.2, 3ms = 9, 5s$$

Dans le cas où BP1 est activé, le compteur U1 réalise environ 3 rotations complètes par seconde, ce qui permet de positionner U1 sur une position intermédiaire aléatoirement.

Une fois le bouton poussoir relâché, le sujet pour lequel on teste le temps de réaction ignore le moment où va se présentera un front montant sur la sortie  $Q_{11}$ , cette durée varie entre 0 et 9,5s.

3. Analyse du circuit : 44

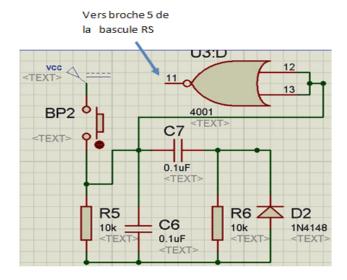

#### 3.2 Circuit de déclenchement

Le circuit formé par  $C_1$ ,  $R_{13}$  et  $D_2$  est un dérivateur.

Au front montant du signal dérivé à la sortie  $Q_{11}$ ,  $C_1$  se charge rapidement à travers  $R_{13}$  entrainant l'apparition d'une brève impulsion positive sur la cathode de la diode  $D_2$ , l'impulsion obtenue est acheminée sur l'entrée d'une bascule RS formé par la porte U8 :A dont la sortie est dirigée vers l'entrée de la porte U8 :B du circuit intégré U8 qui est le circuit intégré CD4001 comportant quatre portes NOR. Dès qu'un état haut se présente sur l'entrée "1"de la porte U8 :A. la sortie "4"de la porte U8 :B passe à un état haut stable à condition que l'entrée "5"soit soumise à un état bas.

Tant que le bouton poussoir BP2 n'est pas sollicité, les entrées de la porte U8 :D de U8 restent à un état bas et l'entrée "5" de la bascule RS est soumise à un état haut. La bascule RS est alors insensible aux impulsions positives issues du dérivateur.

Dès qu'on appuie sur le bouton poussoir BP2, la bascule RS fonctionne car l'entrée "5" est à un état bas.

Au bout d'une durée qui peut varier de 0 à 9,5 secondes, la sortie de la bascule passe alors à l'état haut, ainsi la sortie de la porte U5 :B de U5 passe à l'état bas permettant d'activer U2, et la sortie de la porte U5 :A de U5 passe à l'état haut provoquant l'allumage de la DEL D1.

#### 3.3 Chronométrage du temps de reflexe

Le circuit intégré U2 qui est le CD4060 est un compteur binaire constitué de quatorze étages montés en cascade et d'un oscillateur interne dont la période dépend de la valeur de la capacité  $C_8$  et de la résistance variable RV2.

Le compteur est bloqué tant que l'entrée reset de U2 est à un niveau haut, dans ce cas toutes ses sorties sont à un état bas.

Dès que l'entrée 'reset' de U2 passe à l'état bas, l'oscillateur fonctionne, selon la valeur de la résistance ajustable, la période du signal obtenu sur la branche "9" du compteur U2 peut varier de  $10\mu$  s à  $0.35\,\mathrm{ms}$ . Les signaux de comptage sont alors prélevés sur la sortie  $Q_4$  du compteur U2. Le chronométrage cesse dès que le sujet test relâche BP2 et c'est à ce moment que l'entrée de contrôle de la bascule RS est de nouveau à l'état bas entrainant le blocage de U2.

#### 3.4 Comptage numérique

U4 est un double compteur BCD. Le premier compteur dont l'entrée de comptage est la broche "2"('Enable A') est affecté au comptage des unités.

3. Analyse du circuit : 45

L'entrée "10" ("Enable B") du second compteur B est reliée à la sortie  $Q_3$  du compteur U4 :A. le compteur U4 :B permettra alors de compter les dizaines. Au moment où le sujet test appuie sur BP2, le dérivateur formé par  $C_3$ ,  $R_{11}$  et  $D_3$  transmet une brève impulsion positive sur les entrées "reset "de deux compteurs U4 :A et U4 :B, ce qui assure l'initialisation à zéro de ces deux compteurs qui fonctionnent que si leurs horloges sont à un niveau bas.

Lorsque le comptage atteint la valeur "99", soit "1001 1001", les portes U5 :C et U5 :D et U5 présentent un état bas à leur sortie et la sortie de la porte U8 :C passe à un niveau haut, il en est de même pour l'horloge ' "CLOCK A "entrainant le blocage du compteur sur la position 99 impliquant ainsi que le sujet a un très mauvais temps de réactions.

#### 3.5 Affichage

U3 et U7 sont des décodeurs BCD 7-segments dont les sorties sont reliées par l'intermédiaire des résistances de limitation aux entrées des afficheurs à cathode commune.

Les résultats du test s'affichent alors aussitôt que le bouton poussoir BP2 est relâché.

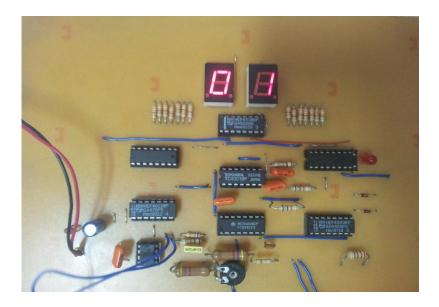

#### 4 Résultats et interprétations

Dans cette partie seront présentés quelques résultats pratiques obtenus en invitant quelques collègues et camarades à faire ce test de temps de réaction.

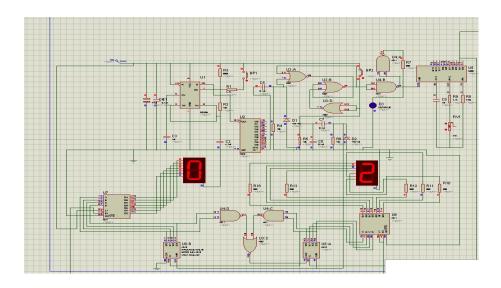

A La mise sous tension du circuit, les afficheurs affichent la valeur  ${\bf 0}$  comme le montre la figure 3.7 suivante :

FIGURE 3.7 – La mise sous tension du testeur de temps de réaction.

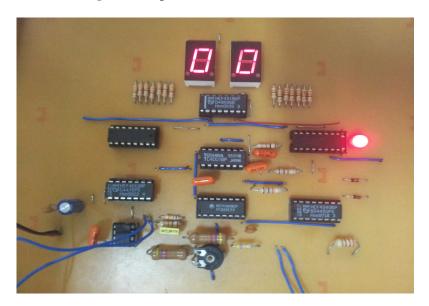

Dans un premier temps, on appuie sur le bouton poussoir BP1, ensuite sur le bouton poussoir BP2, on voit dans ce cas que la DEL s'allume et le résultat obtenu est représenté dans la figure 3.8 qui suit :

FIGURE 3.8 – Allumage de la DEL par action sur les deux boutons poussoirs BP1 et BP2.

Après l'allumage de la DEL, le bouton poussoir BP1 est relâché, et le sujet test attend l'extinction de la DEL, lorsque cette dernière s'éteint, le sujet doit relâché le bouton BP2.

**Premier test** Le premier test a été réalisé sur nous. Les résultats obtenus sont représentés les figures 3.9 et 3.10 suivantes :

FIGURE 3.9 – Test de de temps de réaction sur Mr. BRIXI NIGASSA Med El Amine.

FIGURE 3.10 – Test de temps de réaction sur Mr. Taberkit Med Amine.

Dans cas on peut remarquer que le temps de réaction est d'une durée d'une seconde, on peut dire alors que le temps de réaction est bon, et de ce fait on peut déduire que les deux sujets test ont passé le test en étant dans un bon état physique

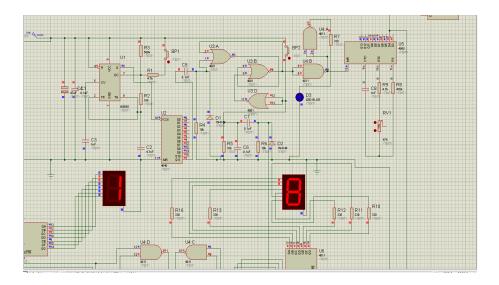

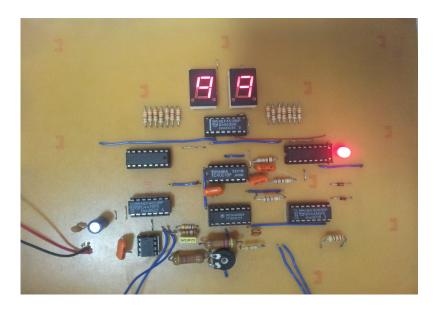

**Deuxième test** Dans ce deuxième test, on va essayer de retarder le temps de réaction, les résultats obtenus sont représentés sur la figure 3.11 suivante :

FIGURE 3.11 – Réponse du troisième sujet test après 10 secondes.

Dans ce cas le sujet test répond après une durée de 10 secondes, ce qui représente une durée de réaction assez importante, ce qui induit que le sujet test présente un mauvais temps de réaction.

Le dernier test En augmentant cette durée de réponse, on obtient une durée de 99 secondes comme le montre la figure suivante :

FIGURE 3.12 – Réponse du dernier sujet test après 99 secondes.

Donc ce qu'on peut dire ici, c'est que le sujet test présente un très mauvais temps de réaction par rapport à un individu normal.

#### 5 Conclusion

Nous avons pu constater dans ce chapitre l'utilité de notre système, le but étant de mesurer le temps de réaction d'un individu donné, on peut déduire à partir des résultats satisfaisant obtenus, que notre système est apte à détecter si le sujet test présente un temps deréaction normal ou non, ainsi on pourra détecter l'état de l'individu, mais aussi détecter éventuellement un début de maladie chez l'individu en question.

Nous avons pu ainsi valider nos résultats pratiques en les comparant aux résultats de simulation que nous avons obtenus par le biais du logiciel ISIS.

Les résultats de simulation ainsi que les résultats pratiques sont jugés satisfaisant et assez prometteurs .

5. CONCLUSION 49

## Conclusion et Perspectives

Le principal objectif de ce mémoire était de faire l'étude et la réalisation d'un testeur de temps de réaction.

L'étude d'un tel sujet a nécessité la présentation dans un premier temps de quelques bases de l'électronique générale ainsi que l'électronique numérique notamment les circuits astables, les portes logiques, les bascules ainsi que le principe des afficheurs 7-segments.

Par la suite nous avons présenté notre système, et nous avons fait l'étude électrique ainsi que la simulation, et grâce aux résultats obtenus, nous avons pu confirmer le bon fonctionnement de notre système, malgré un léger problème d'exécution en temps réel sous le logiciel Proteus ISIS, par la suite on est passé à la réalisation pratique de notre système sur circuit imprimé, ce qui nous a permis de conforter les résultats de simulation obtenus, mais aussi de faire des tests plus poussé sur différents individus afin de voir et de constater la différence du temps de réaction de chacun de ces individus.

Les résultats obtenus sont très satisfaisant d'une part grâce au temps de réponse très rapide de notre système, et d'autre part ça nous a permis de détecter l'état dans laquelle se trouve l'individu, comme la fatigue par exemple mais aussi le paramètre de l'âge qui joue aussi un rôle important aussi. La détection précoce de maladie aussi peut être détecté par notre système, en faisant le test sur un individu en bonne santé à priori, mais présentant un temps de réaction assez lent par rapport à la normale.

Tout cela a permis de voir qu'avec un système simple comme le nôtre, facile à réaliser, on pourrait avoir une détection du temps de réaction assez précise et ainsi prévenir des différents risques pouvant être entrainés à cause de ce dernier, qu'ils soient des risques médicales, risques d'accidents de la circulation, ou bien d'autres risques pouvant avoir des conséquences sur l'individu lui-même ou sur d'autre individus.

Comme perspectives, nous proposons aux intéressés de compléter ce dispositif en lui ajoutant une partie sonore qui aura pour but de constater la réaction d'un sujet test à un son donné. On peut perfectionner la mesure du temps de réaction en rajoutant d'autres diodes DEL ainsi que d'autres boutons poussoirs, ces derniers seront contrôlés par un microcontrôleur qui enverra les résultats vers un afficheurs 7-segments ou éventuellement un afficheur LCD.

## Bibliographie

- [1] J.-C. MICHEL, "La fonction gration dun signal rectangulaire," Cours Traitement du signal :http://www.gecif.net/articles/genie\_ electrique/cours/terminale/cours/les\_montages\_astables.pdf, Tech. Rep., 2013. [Online]. Available: http://www.gecif.net/articles/genie\_electrique/cours/terminale/cours/les\_montages\_astables.pdf

- [2] P. DUBUC and M. NEBRA, "Portes logiques," Simple IT, cours sur les portes logiques: http://www.siteduzero.com/informatique/tutoriels/fonctionnement-d-un-ordinateur-depuis-zero/portes-logiques, Tech. Rep., access 2013. [Online]. Available: http://www.siteduzero.com/informatique/tutoriels/fonctionnement-d-un-ordinateur-depuis-zero/portes-logiques

- [3] M. GRAILLAT, "électronique : le classeur -," Cours Électronique / Physique : http://amoweb.fr/fichiers/electronique/electronique.pdf, Tech. Rep., 2010. [Online]. Available : http://amoweb.fr/fichiers/electronique/electronique.pdf

- [4] M. HADJILA, "Logique combinatoire et sentielle," Cours dingorat en ctronique, module TEC480: Electronique Numque., Tech. Rep., 2007.