# REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

## UNIVERSITE ABOU BEKR BELKAID-TLEMCEN FACULTE DE TECHNOLOGIE

#### DEPARTEMENT DE GENIE ELECTRIQUE ET ELECTRONIQUE

#### Mémoire

Pour l'obtention du diplôme de Master en Instrumentation

#### **Thème**

## Réalisation d'un générateur de signaux pseudo-aléatoire Numériques et Analogiques

#### Présentée par :

#### Mr CHAREF ABDELLATIF Mr SENINI AYYOUB

Soutenue en 26 mai 2016 devant les membres du jury :

BOUAZZA BENYOUNES MCA U.Tlemcen Président

MOULAI KHATIR Ahmed Nassim MCB U.Tlemcen Examinateur

BOUAZZA née GUEN Ahlam Professeur U.Tlemcen Encadreur

Année Universitaire: 2015/2016

## Remerciements

Avant tout, il ne saurait question d'entreprendre les remerciements sans avoir remercié Le BON DIEU de nous avoir permis de réaliser ce travail.

#### Nous tenons à remercier :

Tout d'abord à nos chers parents, d'avoir été là toutes ces années de nous avoir aidé à faire ce très long parcours, et de nous avoir guidé vers le droit chemin.

Nous remercions infiniment notre encadreur **Mme A.GUEN BOUAZZA** pour sa confiance, pour son aide si précieuse et surtout infini, pour son coté humain, son indulgence, toute sa compétence, sa compréhension et surtout son immense patience qui nous a permis d'achever ce modeste travail. Nous lui témoignons ainsi toute notre gratitude pour toute son aide.

Nous adressons aussi nos remerciements à **Mr B.BOUAZZA** qui nous a fait l'honneur de présider le jury de notre mémoire.

Nous remercions aussi **Mr. N.MOULAY KHATIR** qui a aimablement accepté de juger ce travail.

Nous tenons à remercier tous les membres du Laboratoire de d'Electronique pour leurs soutiens inconditionnels et leur aide si précieuse qui a permis a l'aboutissement de ce modeste Travail.

Enfin, à toutes les personnes ayant participé de prés ou de loin à la réalisation de ce projet, un grand merci.

## Dédicaces

Au nom de dieu, le clément, le très miséricordieux

Je dédie ce modeste travail à :

Mes *parents*, en témoignage de l'amour, du respect et de la gratitude que je leur porte.

Je ne pourrai qu'exprimer un infini remerciement à mes parents qui n'ont jamais arrêté de M'encourager et de m'aider à aller de l'avant.

A mes adorables sœurs et mon très cher frère pour leurs encouragements, amour et aide.

A tous mes *oncles* et *tantes* sans exception

A tous mes *cousins* et *cousines*

A tous mes amis (es)

**CHAREF ABDELLATIF**

## Dédicaces

Au nom de dieu, le clément, le très miséricordieux

Je dédie ce modeste travail à :

Mes *parents*, en témoignage de l'amour, du respect et de la gratitude que je leur porte.

Je ne pourrai qu'exprimer un infini remerciement à mes parents qui n'ont jamais arrêté de M'encourager et de m'aider à aller de l'avant.

A mes adorables sœurs et mon très cher frère pour leurs encouragements, amour et aide.

A tous mes *oncles* et *tantes* sans exception

A tous mes *cousins* et *cousines*

A tous mes amis (es)

# Sommaire

## Introduction générale

| Chapitre I : étude d'un générateur aléatoire numérique |     |

|--------------------------------------------------------|-----|

| 1. Les Portes logiques                                 | . 1 |

| 1.1. Portes logiques de base                           | . 2 |

| 1.1.1. Inverseur                                       | . 2 |

| 1.1.2. Porte AND                                       | . 2 |

| 1.1.3. Porte OR                                        | . 3 |

| 1.2. Combinaisons de portes logiques                   | . 3 |

| 1.2.1. Porte NAND (Non ET)                             | . 3 |

| 1.2.2. Porte NOR (Non OU)                              | . 4 |

| 1.3. Porte XOR                                         | . 5 |

| 1.4. Porte NXOR                                        | . 5 |

| 2. Les multivibrateurs astables                        | . 6 |

| 2.1. Différents montages astable                       | . 7 |

| 2.1.1. Montage à base de transistors                   | . 7 |

| 2.1.2. Montage Astable à ampli opérationnel            | . 9 |

| 2.1.2.1. Principe de fonctionnement                    | 10  |

| 2.1.3. Montage astable à circuit intégré NE555         | 11  |

| 2.1.4. Montage astable à porte logique                 | 13  |

| 3. Filtres électronique                                | 16  |

| 3.1. Définitions.                                      | 16  |

| 3.2. Types de filtres                                  | 17  |

| 4. Trigger de Schmitt                                  | 18  |

| 4.1. Fonctionnement                                    | 19  |

| 5. le transistor bipolaire                             | 20  |

| 5.1. Constitution                                      | 20  |

| 5.2. Principe de fonctionnement                        | 21  |

| 5.3. Les régimes de fonctionnement                     | 22  |

| 5.3.1. Les régimes de blocage (état bloqué)            | 22  |

| 5.3.2. Régime linéaire (amplificateur)                 | 23  |

| 5.3.3. Régime de saturation (état passant)             | 23  |

| 5.4. Le transistor en commutation (interrupteur statique)                                                                                                                                                                                                                                                                                                                                                                                                                        | 24                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| 5.5. Le transistor BD139                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 24                                           |

| 5.5.1. Caractéristiques électriques du transistor BD139                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                           |

| 5.6. Le transistor BC547                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                                           |

| 5.6.1. Caractéristiques électriques du transistor BC547                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                           |

| 5.6.2. Applications du transistor BC547                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                           |

| 6. Montage Darlington                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                                           |

| 6.1. Principe                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26                                           |

| 6.2. Schéma équivalent en petits signaux                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28                                           |

| 6.3. Paramètres du circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28                                           |

| 6.3.1. Résistance d'entrée                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28                                           |

| 6.3.2. Résistance de sortie                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                           |

| 7. Circuit intégré CD4011                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 30                                           |

| 7.1. Caractéristiques                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                           |

| 8. Compteur binaire CD4040                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30                                           |

| 8.1. Caractéristiques                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| Chapitre II : étude d'un générateur aléatoire analogique                                                                                                                                                                                                                                                                                                                                                                                                                         |                                              |

| Chapitre II : étude d'un générateur aléatoire analogique  1. L'amplificateur opérationnel                                                                                                                                                                                                                                                                                                                                                                                        | . 31                                         |

| 1. L'amplificateur opérationnel                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                              |

| L'amplificateur opérationnel      Sénéralités                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31                                           |

| L'amplificateur opérationnel                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31                                           |

| L'amplificateur opérationnel                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 31<br>32<br>33                               |

| L'amplificateur opérationnel      L. Généralités      L. Représentation symboliques de l'amplificateur opérationnel      L. Caractéristiques                                                                                                                                                                                                                                                                                                                                     | 31<br>32<br>33                               |

| 1. L'amplificateur opérationnel                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31<br>32<br>33<br>33                         |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée                                                                                                                                                                                               | 31<br>32<br>33<br>33                         |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie                                                                                                                                                                   | 31<br>32<br>33<br>33<br>34                   |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie  1.4.4. Gain de puissance                                                                                                                                         | 31<br>32<br>33<br>33<br>34<br>34             |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie  1.4.4. Gain de puissance  1.5. Tension de décalage et courants d'entrée.                                                                                         | 31<br>32<br>33<br>33<br>34<br>35             |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie  1.4.4. Gain de puissance  1.5. Tension de décalage et courants d'entrée  1.6. Vitesse de balayage                                                                | 31<br>32<br>33<br>34<br>34<br>35<br>35       |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie  1.4.4. Gain de puissance  1.5. Tension de décalage et courants d'entrée.                                                                                         | 31<br>32<br>33<br>34<br>34<br>35<br>35       |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie  1.4.4. Gain de puissance  1.5. Tension de décalage et courants d'entrée  1.6. Vitesse de balayage  1.7. Réaction positive et contre-réaction.                    | 31<br>32<br>33<br>34<br>34<br>35<br>35<br>36 |

| 1. L'amplificateur opérationnel  1.1. Généralités  1.2. Représentation symboliques de l'amplificateur opérationnel  1.3. Polarisation de l'amplificateur opérationnel  1.4. Caractéristiques  1.4.1. L'impédance d'entrée, de gain et gain en puissance  1.4.2. Impédance d'entrée  1.4.3. Impédance de sortie  1.4.4. Gain de puissance  1.5. Tension de décalage et courants d'entrée  1.6. Vitesse de balayage  1.7. Réaction positive et contre-réaction  1.7.1. Définitions | 31<br>32<br>33<br>34<br>34<br>35<br>35<br>36 |

| 2.1. Amplificateur suiveur de tension                                                   | 38                                           |

|-----------------------------------------------------------------------------------------|----------------------------------------------|

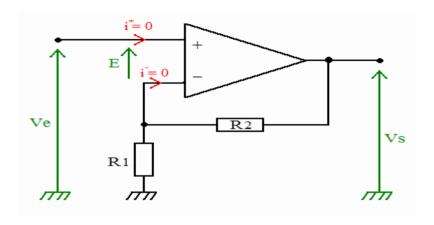

| 2.2. Amplificateur de tension mon-inverseur                                             | 39                                           |

| 2.3 Amplificateur de tension inverseur                                                  | 40                                           |

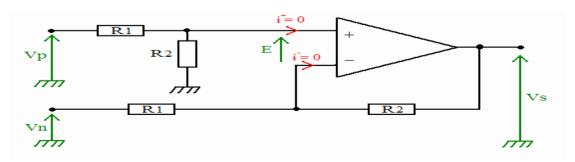

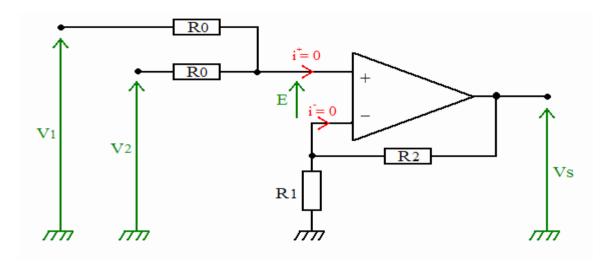

| 2.4. Amplificateur différentiel                                                         | 40                                           |

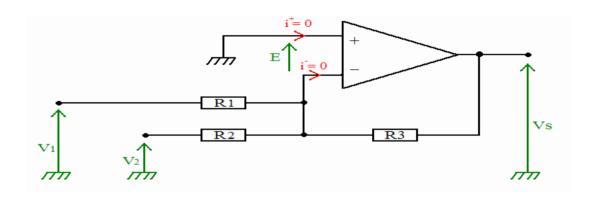

| 2.5. Amplificateur sommateur                                                            | 41                                           |

| 2.6. Additionneur non-inverseur (extensible a n entrées)                                | 42                                           |

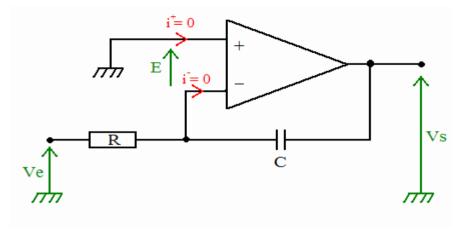

| 2.7. Intégrateur inverseur                                                              | 43                                           |

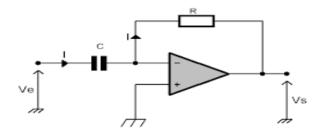

| 2.8. Dérivateur                                                                         | 44                                           |

| 2.9. Comparateur de tensions                                                            | 44                                           |

| 3. Le transistor bipolaire 2N2222                                                       | 45                                           |

| 3.1. Complémentaire des transistors 2N2222                                              | 45                                           |

| 3.2. Caractéristiques électriques du transistor 2N2222                                  | 46                                           |

| 3.3. Applications du transistor 2N2222                                                  | 46                                           |

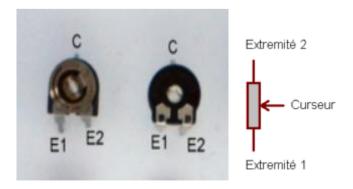

| 4. Potentiomètre                                                                        | 46                                           |

|                                                                                         |                                              |

| Chapitre III : Résultats et interprétations                                             |                                              |

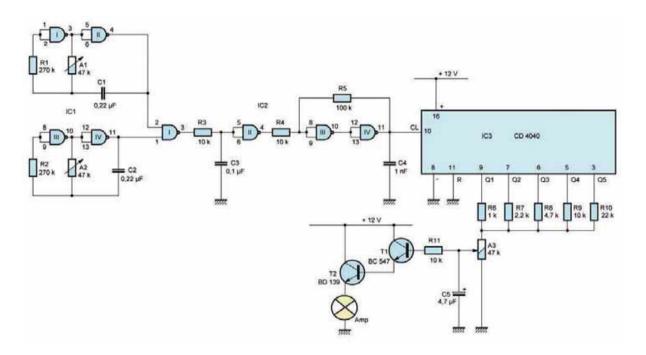

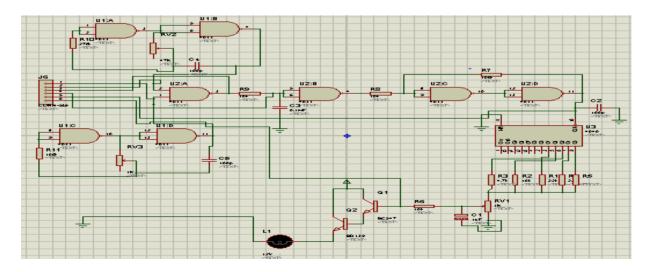

| 1. Analyse du générateur numérique de signaux aléatoires                                | 47                                           |

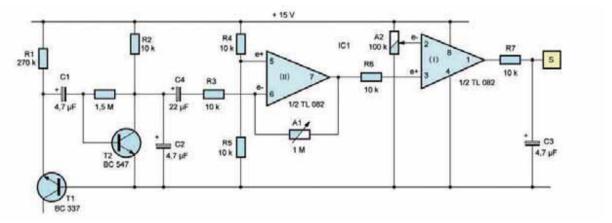

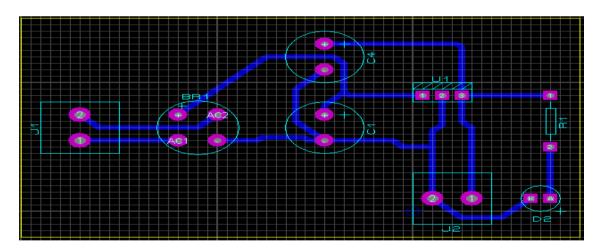

| 2. Analyse du générateur Analogique de signaux aléatoires                               |                                              |

| 3. Chronogrammes aux différents nœuds de nos circuits sont donnés dans ce qu            |                                              |

| suit                                                                                    | <b>5</b> 1                                   |

|                                                                                         | 31                                           |

| 3. 1. Chronogrammes aux différents nœuds de notre circuit numérique                     |                                              |

| 3. 1. Chronogrammes aux différents nœuds de notre circuit numérique                     | 51                                           |

| 3.1.1. Les signaux obtenus dans les différents points du circuit N°1                    | 51<br>55<br>58                               |

| 3.1.1. Les signaux obtenus dans les différents points du circuit N°1                    | 51<br>55<br>58                               |

| 3.1.1. Les signaux obtenus dans les différents points du circuit N°1                    | 51<br>55<br>58<br>60                         |

| <ul> <li>3.1.1. Les signaux obtenus dans les différents points du circuit N°1</li></ul> | 51<br>55<br>58<br>60<br>61                   |

| 3.1.1. Les signaux obtenus dans les différents points du circuit N°1                    | 51<br>55<br>58<br>60<br>61<br>63             |

| 3.1.1. Les signaux obtenus dans les différents points du circuit N°1                    | 51<br>55<br>58<br>60<br>61<br>63<br>64       |

| 3.1.1. Les signaux obtenus dans les différents points du circuit N°1                    | 51<br>55<br>58<br>60<br>61<br>63<br>64<br>65 |

## Liste de figure

| I.1. Symbole d'un inverseur.                                                               | 2  |

|--------------------------------------------------------------------------------------------|----|

| I.2. Porte logique AND                                                                     | 2  |

| I.3. Symbole d'une porte OR                                                                | 3  |

| I.4. Porte NAND                                                                            | 4  |

| I.5. Symbole d'une porte NOR                                                               | 4  |

| I.6. Symbole d'une porte XOR                                                               | 5  |

| I.7. La porte NXOR                                                                         | 5  |

| I.8. Astable à base de transistors                                                         | 7  |

| I.9. Chronogrammes aux différents nœuds de l'astable à base de l'astable à de transistors. |    |

| I.10. Astable à base de l'amplificateur opérationnel                                       | 9  |

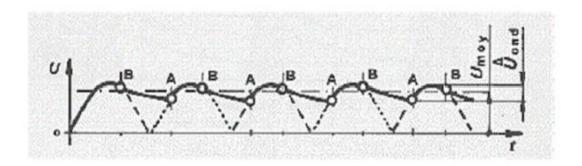

| I.11. Tensions aux nœuds A et B de l'astable                                               |    |

| I.12. Astable à base du NE 555                                                             | 12 |

| I.13. Astable à 2 portes logiques CMOS inverseuses                                         | 13 |

| I.14. Circuit équivalent entre les nœuds S et H                                            | 14 |

| I.15. Filtre passe-haut du premier ordre                                                   | 17 |

| I.16. Filtre passe-bas du premier ordre.                                                   | 17 |

| I.17. Filtre passe- bande.                                                                 | 18 |

| I.18. Signaux réel à l'entrée et à la sortie de l'inverseur                                | 19 |

| I.19. Signaux à l'entrée et à la sortie d'un trigger de schmitt                            | 19 |

| I.20. Cycle d'hystérésis d'une bascule de schmitt                                          | 20 |

| I.21. Transistor NPN et PNP                                                                | 21 |

| I.22. Transistor NPN                                                                       | 21 |

| I.23. Régime de conduction.                                                                | 22 |

| I.24. Transistor équivalent à un interrupteur ouvert                                       | 22 |

| I.25. Caractéristiques du transistor                                                       | 23 |

| I.26. Transistor équivalent à un interrupteur fermé                                        | 24 |

| I.27. Transistor BD139.                                                                    | 25 |

| I.28. Montage Darlington                                                                   | 27 |

| I.29. Schéma équivalent du transistor Darlington en régime petits signaux.                 | 28 |

| I.30. Schéma équivalent simplifié permettant de déterminer la résistance de sortie. | 20   |

|-------------------------------------------------------------------------------------|------|

|                                                                                     |      |

| II.1. Symbole européen de l'amplificateur opérationnel                              |      |

| II.2. Symbole américain de l'amplificateur opérationnel                             |      |

| II.3. Symbole simplifié de l'amplificateur opérationnel.                            |      |

| II.4. Polarisation de l'amplificateur opérationnel.                                 |      |

| II.5. Schéma interne de l'AOP.                                                      |      |

| II.6. Modélisation d'un AOP comprenant les impédances d'entrées et de sortie        |      |

| II.7. Conséquence de l'offset (Ua=Vs).                                              | . 36 |

| II.8. Effet du slew-rate                                                            |      |

| II.9. Réaction positive et contre-réaction                                          |      |

| II.10. Amplificateur suiveur de tension                                             |      |

| II.11. Amplificateur de tension non-inverseur                                       |      |

| II.12. Amplificateur de tension inverseur.                                          |      |

| II.13. Amplificateur différentiel.                                                  |      |

| II.14. Amplificateur sommateur.                                                     |      |

| II.15. Amplificateur Additionneur non-inverseur.                                    | . 42 |

| II.16. Intégrateur inverseur                                                        |      |

| II.17. Dérivateur                                                                   |      |

| II.18. Comparateur de tensions                                                      |      |

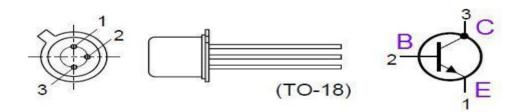

| II.19. Brochage des 2N2222 en boitier TO18                                          |      |

| II.20. Transistor 2N2222.                                                           | . 45 |

| II.21. Schéma d'un potentiomètre ajustable                                          | . 46 |

| III.1. Générateurs de signaux aléatoires d'origine logique                          | . 47 |

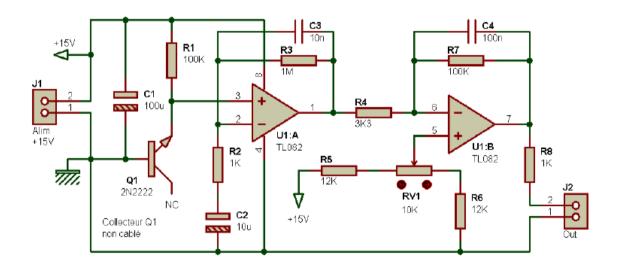

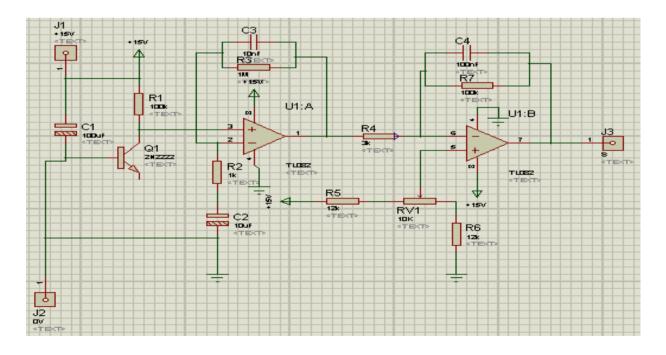

| III.2. Générateurs de signaux aléatoires analogiques.                               | . 50 |

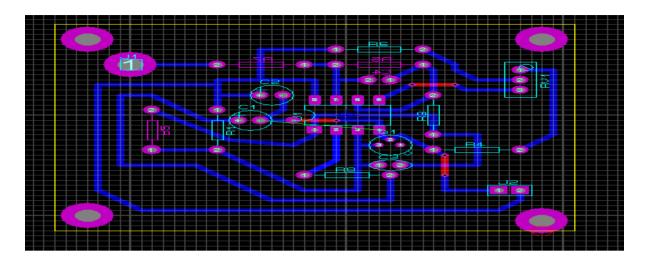

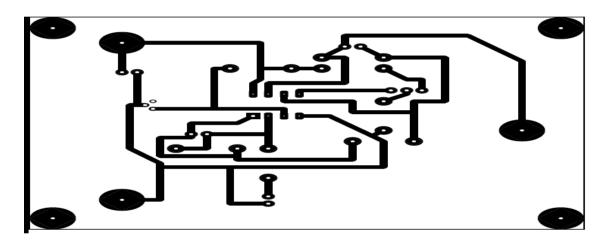

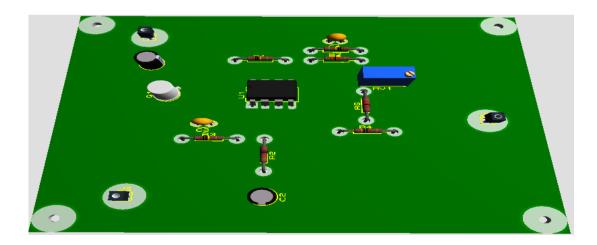

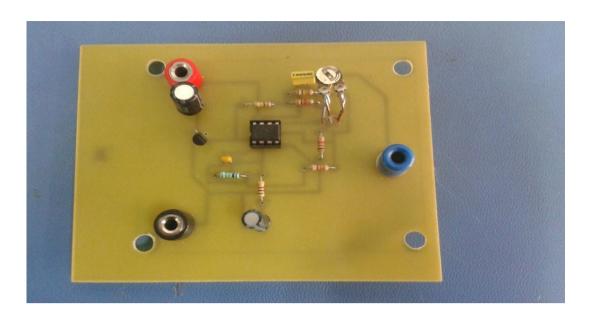

| III.3. Générateurs de signaux aléatoires analogiques réalisés pratiquement          | . 52 |

| III.4. Schéma Isis du circuit N°1 (signaux aléatoires d'origine logique)            | . 53 |

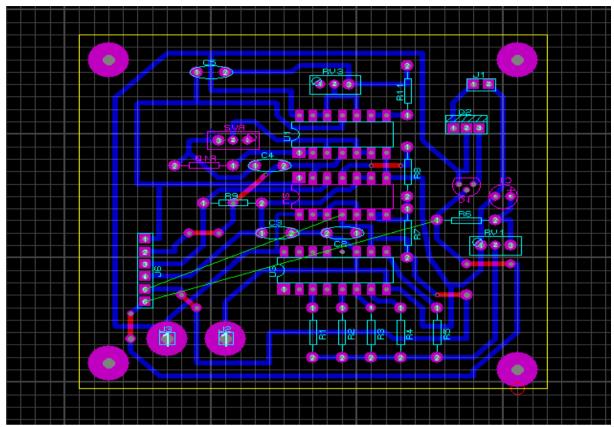

| III.5. schéma de circuit N°1(ares)                                                  | . 54 |

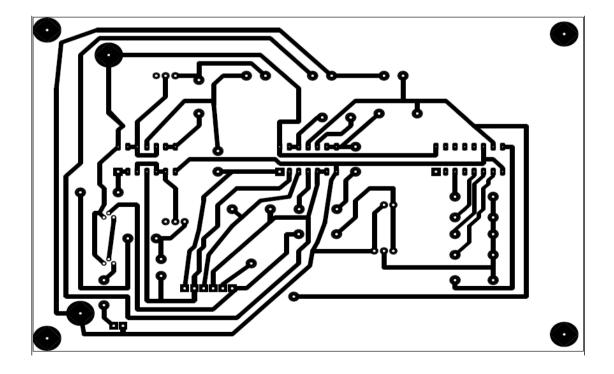

| III.6. Schéma de circuit imprimé N°1                                                | . 54 |

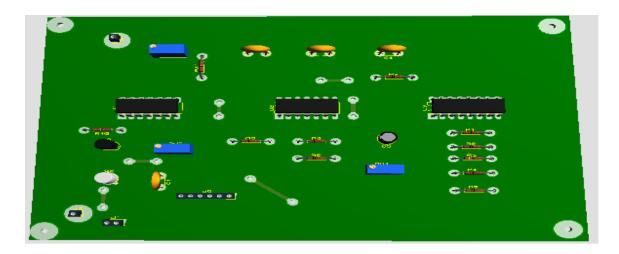

| III.7. Schéma du circuit 3D                                                         | . 55 |

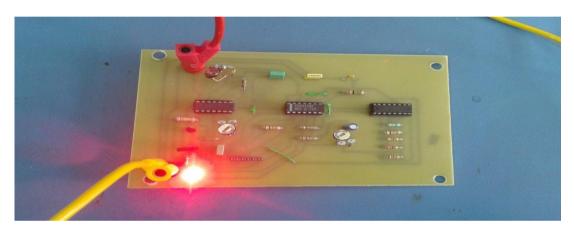

| III.8. Prototype du circuit N°1                                                     | . 55 |

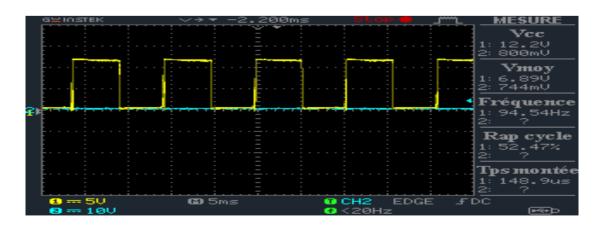

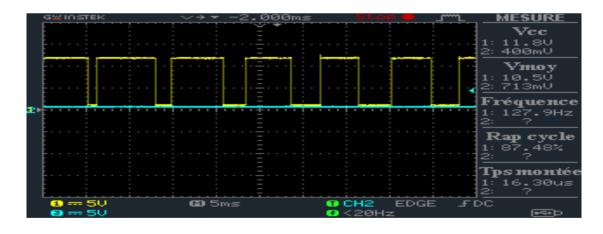

| III.9. Graphe du signal [point N°1]                                                 | . 55 |

|                                                                                     |      |

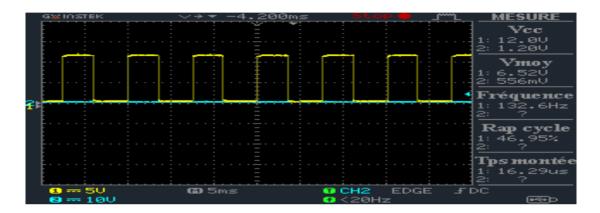

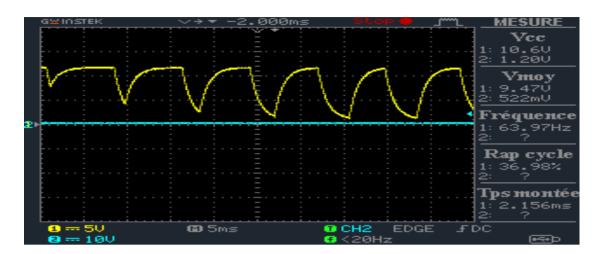

| III.10. Graphe du signal [point N°2]       | 56 |

|--------------------------------------------|----|

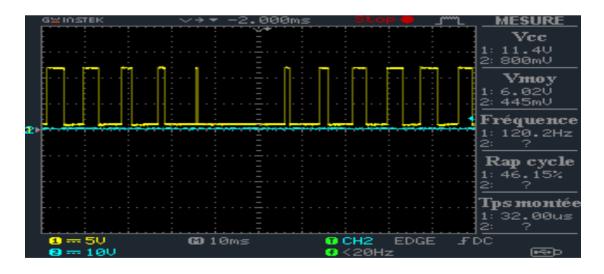

| III.11. Graphe du signal [point N°3]       | 56 |

| III.12. Graphe du signal [point N°4]       | 57 |

| III.13. Graphe du signal [point N°5]       | 57 |

| III.14. Graphe du signal [point N°6]       | 58 |

| III.15. Schéma Isis du deuxième circuit    | 58 |

| III.16. Schéma de circuit N°2(ares)        | 59 |

| III.17. Schéma de circuit imprimé N°2      | 59 |

| III.18. Schéma du circuit 3D.              | 59 |

| III.19. Prototype du circuit N°2.          | 60 |

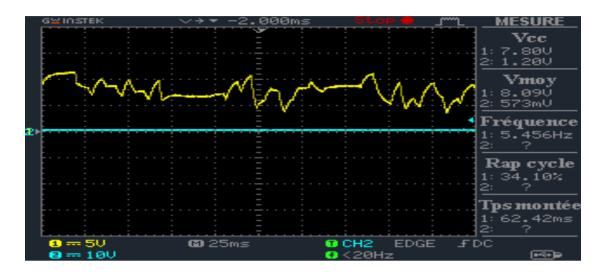

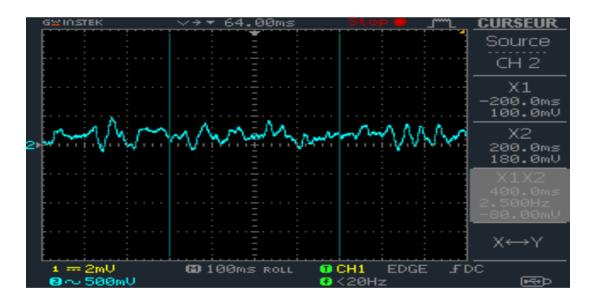

| III.20. Schéma signal Bruit du circuit N°2 | 60 |

|                                            |    |

## Liste des tableaux

| Table I.1. Table de vérité de l'inverseur                  | 2  |

|------------------------------------------------------------|----|

| Table I.2. Table de vérité de la porte AND.                | 3  |

| Table I.3. Table de vérité de la porte OR                  | 3  |

| Table I.4. Table de vérité de la porte NAND.               | 4  |

| Table I.5. Table de vérité de la porte NOR.                | 4  |

| Table I.6. Table de vérité de la porte XOR                 | 5  |

| Table I.7. Table de vérité de la porte NXOR                | 5  |

| Table II.1. Table de correspondance entre entrée et sortie | 43 |

## Introduction générale

On appelle générateurs de bruit, tout dispositif électronique pour lequel la grandeur de sortie serait une grandeur qui pourrait prendre une valeur quelconque dans un ensemble spécifié.

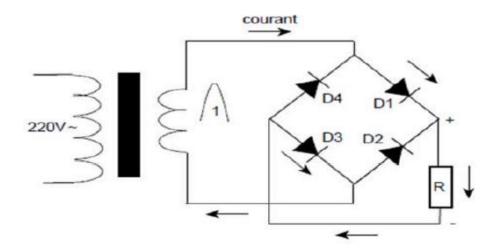

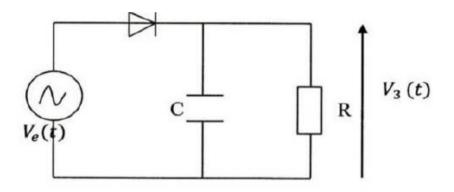

Ce type de générateur pourrait être totalement analogique, ou dans ce cas la source de bruit pourrait être tout simplement une résistance et le bruit serait un bruit thermique, ca pourrait aussi être un transistor bipolaire ou une diode et on aurait alors dans ce cas parler d'un bruit de jonction.

Il est bien clair que la liberté sans limite des phénomènes aléatoires ne fait indéniablement pas bon ménage avec la rigueur et la fermeté de l'électronique, il est cependant possible de créer des signaux aléatoires ou pseudo-aléatoires qui échappent tant bien que mal à cette rigueur et c'est justement pour cela que ce type de générateurs est conçu.

C'est ainsi que notre travail a consisté à étudier deux types de générateurs de signaux aléatoires le premier faisant appel à la logique binaire alors que le second repose en fait sur un principe analogique.

C'et ainsi que notre mémoire se divise en trois chapitres:

Le premier chapitre a été consacré à l'étude d'un générateur aléatoire numérique faisant appel à la logique binaire, nous présentons alors dans ce premier chapitre le fonctionnement des différents constituants de ce générateur.

Au second chapitre, nous présentons notre générateur de signaux aléatoires analogique et présentons le fonctionnement des différents constituants de ce second générateur.

Notre dernier chapitre est principalement destiné à l'analyse de nos deux circuits

Comme cité en introduction, notre travaille a consiste à étudier deux générateurs de signaux aléatoire le premier numérique et le second analogique.

Nous présentons dans ce chapitre tous les éléments constituante générateur aléatoire numérique ce dernier cet constitue de :

- Les ports logiques (ports NAND)

- Les multivibrateurs astables

- Filtres électronique

- Trigger de schmitt

- Transistor bipolaire (type BD139 et BC547)

- Montage Darlington

- Compteur binaire CD4040

- Circuit intégré CD4011

Nous allons dans ce qui suit présenté tous les éléments de ce générateur numérique

#### 1. Les Portes logiques :

Tous les circuits sont composés d'un nombre limité de circuits logiques, ces circuits logiques sont aussi appelés « portes logiques ». Nous allons décrire dans ce qui suit ces fonctions logiques de base qui permettent de réaliser des circuits logiques. La réalisation physique de ces portes logiques a beaucoup évolué au cours des dernières années passant du relais mécaniques, puis tubes à vide électroniques, jusqu'aux circuits intégrés. Les portes logiques sont considérées comme des circuits qui combinent les signaux logiques présentés à leurs entrées sous forme de tensions. On aura alors par exemple une tension de 5V pour représenter l'état logique 1 et une tension de 0V pour représenter l'état 0.

Les trois fonctions de base sont la fonction AND, OR, NOT, toutes les autres fonctions peuvent être déduites de ces fonctions principales.

#### 1.1. Portes logiques de base

#### 1.1.1. Inverseur

Cette porte logique agit sur un seul bit. Sa fonction est d'inverser tout simplement le bit d'entrée.

$$S = \overline{A} \tag{I.1}$$

Son symbole est donné par la figure I.1.

Figure I.1: Symbole d'un inverseur [1].

Sa table de vérité est donnée par la table I.1.

| A | S |

|---|---|

| 0 | 1 |

| 1 | 0 |

Table I.1:Table de vérité de l'inverseur.

#### 1.1.2. Porte AND

Cette porte contrairement à la précédente, comprend deux entrées et une seule sortie.

Dans ce cas on effectue une fonction ET logique entre les deux entrées.

$$S = A.B ag{I.2}$$

Symbole est donné par la figure I.2.

Figure I.2: Porte logique AND [1].

Sa table de vérité est donnée par la table I.2.

| A | В | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Table I .2: Table de vérité de la porte AND.

#### **1.1.3. Porte OR**

La sortie S obtenue est le résultat d'un OU logique entre les deux entrées :

$$S = A + B \tag{I.3}$$

Son symbole est donné par la figure I.3.

Figure I.3: Symbole d'une porte OR [1].

Sa table de vérité est donnée par la table I.3

| Entrée 1 | Entrée 2 | Sortie |

|----------|----------|--------|

| 0        | 0        | 0      |

| 0        | 1        | 1      |

| 1        | 0        | 1      |

| 1        | 1        | 1      |

Table I.3: Table de vérité de la porte OR.

#### 1.2. Combinaisons de portes logiques

Ces trois fonctions logiques de base peuvent être combinées afin de réaliser des opérations plus élaborées et ceci en interconnectant les entrées et les sorties des portes logiques.

#### 1.2.1. Porte NAND (Non ET)

Cette porte présente la particularité de pouvoir recréer des portes AND, OR, NON.

Dans un circuit électronique en utilisant seulement des montages composés uniquement de portes NAND. On effectue toujours une opération ET logique entre les deux sorties mais cette fois le résultat obtenue est inverse.

$$S = \overline{A.B} \tag{I.4}$$

Son symbole est donné par la figure I.4.

Figure I.4: Porte NAND [1].

Sa table de vérité est donnée par la table I. 4.

| A | В | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table I.4: Table de vérité de la porte NAND.

#### 1.2.2. Porte NOR (Non OU)

Ici la sortie S obtenue sera le résultat inverse d'un OU logique entre les deux entrées :

$$S = \overline{A + B} \tag{I.5}$$

Son symbole est donné par la figure I.5.

Figure I.5: Symbole d'une porte NOR [1].

Sa table de vérité est donnée par la table I.5.

| Entrée 1 | Entrée 2 | Entrée 3 |

|----------|----------|----------|

| 0        | 0        | 1        |

| 0        | 1        | 0        |

| 1        | 0        | 0        |

| 1        | 1        | 0        |

Table I.5: Table de vérité de la porte NOR.

## 1.3. Porte XOR

$$S = A + B \tag{I.6}$$

Son symbole est donné par la figure I.6.

Figure I.6: Symbole d'une porte XOR [1].

Sa table de vérité est donnée par la table I.6.

| A | В | S |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table I.6: Table de vérité de la porte XOR.

$$S = a\overline{b} + \overline{a}b \tag{I.6}$$

#### 1.4. Porte NXOR

Elle exécute la fonction inverse du OU exclusif :

$$S = \overline{A \oplus B} \tag{I.7}$$

Son symbole est donné par la figure I.7.

Figure I.7: La porte NXOR [1].

Sa table de vérité est donnée par la table I.7.

| A | В | S |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Table I.7: Table de vérité de la porte NXOR.

$$S = \overline{a}b + ab \tag{I.7}$$

#### • Remarque

Nous nous intéressons plus aux portes logiques NAND, car cette porte est utilisée dans le circuit intégrée CD4011, que nous avons utilisé dans notre montage.

#### 2. Les multivibrateurs astables

Les multivibrateurs sont des montages destinés à générer en sortie une tension rectangulaire. Les niveaux hauts et bas des tensions de sortie sont plus ou moins stables. En fonction de cette stabilité, on peut de ce fait distinguer :

- Les multivibrateurs astables.

- Les multivibrateurs monostables.

- Les multivibrateurs bistables.

On s'intéresse dans notre étude aux multivibrateurs astables que nous avons utilisés dans notre réalisation.

Les astables, générateurs de signaux rectangulaires, sont donc des autososcillateurs, car ces circuits ne reçoivent aucune impulsion de l'extérieur contrairement aux monostables et les bistables qui sont considérés comme des oscillateurs de déclanchement.

On remarque alors que tous les multivibrateurs comportent essentiellement:

- Un élément actif tel que le transistor, l'amplificateur opérationnel, les portes logiques ...........

- Un organe qui permettra l'accumulation de l'énergie tel que le condensateur.

- Un organe qui dissipera de l'énergie tel que la résistance.

En fonction de l'élément actif, on distingue donc différents multivibrateurs soit alors à transistor, à porte logiques et enfin les multivibrateurs à circuit intégré tel que le NE555 ou à base d'amplificateur opérationnel.

Un astable ou horloge ne possède donc aucun état stable et par conséquent aucune entrée de déclenchement .Ce dispositif charge d'état spontanément sans qu'il soit nécessaire de lui appliquer une impulsion de commande après avoir gardé l'état actif pendant un temps TH et repasse spontanément à un état inactif pendant un temps TL et ainsi de suite. L'astable est donc considéré comme un oscillateur non-sinusoïdal puisqu'il délivre à sa sortie un signal rectangulaire caractérisé par sa période T et sont rapport cyclique  $B=T_H/T$ , où  $T_H$ : durée du niveau haut.

Il existe différents montages astables, que nous passerons en vu brièvement dans ce qui suit.

#### 2.1. Différents montages astable

#### 2.1.1. Montage à base de transistors

On présente l'astable à base de transistors.

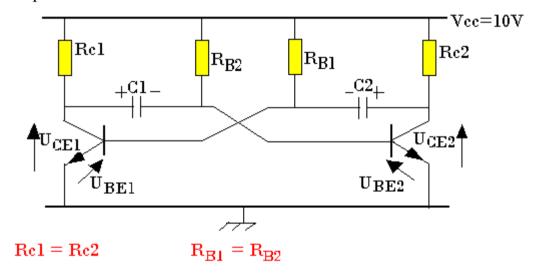

Figure I.8: Astable à base de transistors [2].

On suppose que les condensateurs sont complètement déchargés au départ.

Apres avoir alimenté notre circuit, les deux condensateurs  $C_1$ et  $C_2$  se chargent à travers les résistances  $R_{C1}$  et  $R_{C2}$  et les jonctions "base-émetteur". Les deux transistors  $T_1$  et  $T_2$  tendent à se saturer.

On considère le circuit astable à base de transistors. La sortie de  $T_2$  est reliée à l'entrée de  $T_1$  par une liaison capacitive et réciproquement. Les résistances des

collecteurs sont beaucoup plus faibles que les résistances des bases. On suppose que  $T_1$  se sature en premier : le potentiel de son collecteur passe brutalement de  $V_{cc}$  (tension de polarisation) à $V_{CE1}=0$ . L'armature positive de  $C_1$  est mise à la masse et on a  $V_{C1}+V_{BE2}=0$ ;  $V_{BE2}=-V_{C1}$ . Le transistor  $T_2$  se bloque, le condensateur  $C_2$  va se charger jusqu'à la valeur  $V_{C2}=V_{cc}-0.7$ . Une fois  $C_2$  chargé, la saturation de  $T_1$  est maintenue à travers  $R_{B1}$ .

Le condensateur  $C_1$  est lentement chargé en inverse à travers la résistance  $R_{B2}$  la tension  $V_{C1}$  passe d'une valeur positive à une valeur négative et va tendre vers  $-V_{C1}$  mais cette tension ne va jamais atteindre cette valeur. Pour  $V_{C1}$ =-0,7V, le transistor  $T_2$  va se mettre à conduire et va se saturer, ceci va entraı̂ne que  $V_{CE2}$ =0;  $V_{BE1}$ + $V_{C2}$ =0;  $V_{BE1}$ = $-V_{C2}$  et le transistor  $T_1$  va se bloquer, le condensateur  $C_1$  va se charger rapidement jusqu'à la valeur de  $V_{CC}$ - $V_{BE}$ . Une fois  $C_1$  chargé, la saturation de  $T_2$  est maintenue à travers  $R_{B2}$

Le condensateur  $C_2$  est lentement chargé en inverse à travers  $R_{B1}$ . La tension  $V_{C2}$  passe d'une valeur positive à une valeur négative, lorsque  $V_{C2}$ =-0.7V.  $T_1$  va se remettre à conduire et le cycle recommence.

On remarque alors que le circuit oscille en permanence entre ces deux états. La figure qui suit représente l'évolution des potentiels sur les électrodes des transistors en fonction du temps. La valeur approchée de la période du multivibrateur est égale à :

$$T = 0.7(R_{B2}.C1 + R_{B1}.C2) (I.8)$$

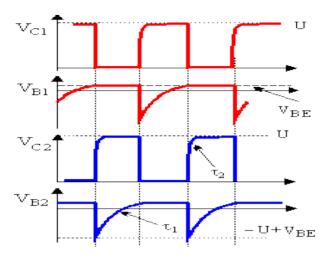

Figure I.9: Chronogrammes aux différents nœuds de l'astable à base de l'astable à base de transistors [2].

#### 2.1.2. Montage Astable à ampli opérationnel

On présente dans la figure suivante le circuit astable à base de l'amplificateur opérationnel.

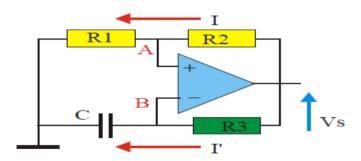

Figure I.10: Astable à base de l'amplificateur opérationnel [2].

figure.11:Tensions aux nœuds A et B de l'astable [2].

#### 2.1.2.1. Principe de fonctionnement

R1 et R2 forment un pont diviseur. Si  $V_A > V_B$ , alors  $V_S = +Vcc$ . Le condensateur C se charge à travers la résistance  $R_3$ . Le potentiel au niveau du point B croit jusqu'à ce qu'il atteigne la valeur  $V_A$ , puis le montage bascule et  $V_S = -Vcc$ .

Le potentiel au point A devient négatif et  $V_A < V_B$ . Le condensateur se décharge à travers la résistance  $R_3$ .  $V_B$  décroit jusqu'à ce qu'il devienne inférieur à  $V_A$  et le montage bascule à nouveau.

Le système va alors osciller interminablement entre ces deux états avec une période qui dépendra essentiellement des valeurs des éléments du circuit.

#### • Calcul de la période

On suppose au départ que Vs = +Vcc (I.9)

$$V_A = \frac{R_1}{R_1 + R_2} \cdot V_S$$

(I.10)

$$R_3 I' = V_S - V_B = R_3 \cdot C \cdot \frac{dV_B}{dt}$$

(I.11)

La solution de l'équation (2) se met sous la forme :

$$V_B = K \exp\left(-\frac{t}{\tau}\right) \tag{I.12}$$

$$\tau = R_3. C \tag{I.13}$$

Une solution particulière est  $V_B = V_S = V_{CC}$

La solution générale est alors la combinaison des deux solutions soit :

$$V_B = K \exp\left(-\frac{t}{\tau}\right) + Vcc \tag{I.14}$$

L'origine du temps est dans notre cas l'instant où le système a basculé et en t=0, on a :

$$V_B(0) = -V_A = -U.\frac{R_1}{R_1 + R_2}$$

(I.15)

$$K = V_B(0) - U = -U \cdot \left[1 + \frac{R_1}{R_1 + R_2}\right] = -U \cdot \frac{2 \cdot R_1 + R_2}{R_1 + R_2}$$

(I.16)

$$V_B = U - U \frac{2R_1 + R_2}{R_1 + R_2} e^{\frac{-t}{\tau}}$$

(I.17)

$En\ t=0: V_B=-U.\frac{R_1}{R_1+R_2}$ ;  $V_B$  Croit jusqu'à t=t1=T/2 pour atteindre la valeur

$$V_B = +U.\frac{R1}{R1 + R2} \tag{I.18}$$

$$U.\frac{R_1}{R_1 + R_2} = U - U.\frac{2.R_1 + R_2}{R_1 + R_2} e^{\frac{-t_1}{\tau}}$$

(I.19)

$$\left[\frac{2.R_1 + R_2}{R_1 + R_2} \cdot e^{\frac{-t1}{\tau}}\right] = \frac{R_2}{R_1 + R_2}$$

(I.20)

$$(2.R_1 + R_2).exp\left(\frac{-t_1}{\tau}\right) = R_2 \implies exp\left(\frac{t_1}{\tau}\right) = 1 + 2.\frac{R_1}{R_2}$$

(I.21)

$$t_1 = \tau . Ln(1 + 2.R_1/R_2)$$

(I.22)

L'expression de la période est donc :  $T = 2R_3$ . C.  $Ln(1 + 2.R_1/R_2)$  (I.23) Ce circuit constitue un oscillateur.

Il permet donc de générer un signal de forme rectangulaire.

#### 2.1.3. Montage astable à circuit intégré NE555

Le NE555 est un circuit intégré à 8 bornes, spécialement conçu pour générer un signal rectangulaire.

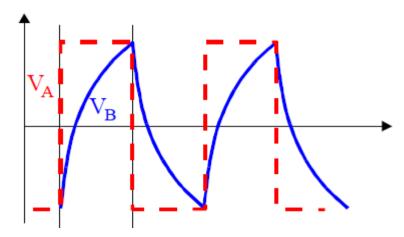

Le câblage du circuit NE555 en astable est donné en figure I.12.

Figure I.12: Astable à base du NE 555[2].

Caractéristiques temporelles du signal de sortie VS:

$$t_H = (R_1 + R_2).C.Ln(2)$$

(I.24)

Dans ce cas le condensateur se charge à travers R1+R2

$$t_B = R_2. C. Ln(2) \tag{I.25}$$

Dans ce cas le condensateur se décharge à travers  $R_2$  seulement.

Les temps de charge et de décharge du condensateur étant différents, le temps haut et le temps bas du signal de sortie  $V_S$  ne sont par conséquent pas égaux. Le temps haut est incontestablement supérieur au temps bas. Il en résulte pour le signal  $V_S$  un rapport cyclique  $\delta$  supérieur à 0,5. Partant des expressions de  $t_H$  et  $t_B$ , on en déduit la période T de sortie  $V_S$  et le rapport cyclique  $\delta$  du signal

$$T = (R_1 + 2.R_2).C.Ln(2)$$

(I.26)

$$\delta = \frac{R_1 + R_2}{R_1 + 2.R_2} \tag{I.27}$$

#### 2.1.4. Montage astable à portes logiques

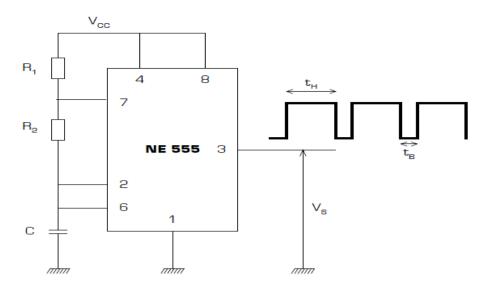

Les portes logiques présentées dans ce mémoire sont technologie CMOS et alimentées entre 0V et  $V_{DD}$ , leur unique seuil de basculement est  $V_{DD}$  /2.

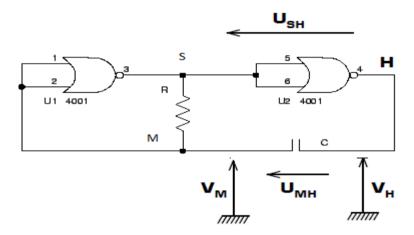

Schéma du montage astable à 2 portes logiques CMOS inverseuses est donné en figure I.13.

Figure I.13: Astable à 2 portes logiques CMOS inverseuses[2].

Hypothèse d'étude et conditions initiales :

$\triangleright$  À t=0 le condensateur C est totalement déchargé ( $U_{MH}$  (0)=0V)

$$V_s = V_{DD}$$

et  $V_H = \mathbf{0}$ v, le circuit commute à  $V_{DD}/2$ .

Les courants d'entrée des portes logiques sont considérés négligeables par rapport au courant de charge du condensateur.

#### Notons que:

•  $V_s$  représente le potentiel du point S par rapport à la masse alors que  $V_H$  représente le potentiel du point H par rapport à la masse. VM représente le potentiel du point M par rapport à la masse,  $U_{MH}$  représente la différence de potentiel entre les points M et H:

$$U_{MH} = V_M - V_H \tag{I.28}$$

•  $U_{SH}$  représente la différence de potentiel entre les points S et H, il s'agit de la tension aux bornes du circuit de charge RC du montage :

$$U_{SH} = V_S - V_H \tag{I.29}$$

- Les tensions  $V_s$  et  $V_H$  ne peuvent prendre que 2 valeurs :  $V_{DD}$  ou 0V :

- Si  $V_s = V_{DD}$ , alors  $V_H = 0$ V, et  $U_{SH} = V_{DD}$ : le condensateur se charge à travers la résistance R, pour atteindre la tension  $V_{DD}$  ()

- Si  $V_s$ =0V, alors

$$V_{H} = V_{DD} \tag{I.30}$$

et

$$\boldsymbol{U_{SH}} = -V_{DD} \tag{I.31}$$

Dans ce cas le condensateur se charge à travers la résistance R pour atteindre la tension  $-V_{DD}$

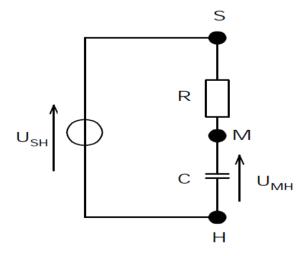

Le montage peut se résumer au circuit de charge suivant, où le générateur de tension  $U_{SH}$  peut prendre 2 valeurs :  $V_{DD}$  ou  $-V_{DD}$  en fonction de l'état de sortie des portes logiques :

Figure I.14: Circuit équivalent entre les nœuds S et H [2].

Analyse du montage et conditions de basculement :

1er cas:

$$V_s = V_{DD} \text{ et } V_H = \mathbf{0}V \tag{I.32}$$

On a donc

$$U_{SH} = V_{DD} \tag{I.33}$$

Le condensateur se charge vers la tension  $V_{DD}$  (et donc  $V_M$  augmente), il en résulte le basculement de la première porte ( $V_s$  passera à 0V) lorsque  $V_M$  atteindra  $V_{DD}/2$ . Comme  $V_H = 0V$ , on a  $U_{MH} = V_M$ . On peut conclure que  $V_s$  basculera à 0V (et  $V_H$  à  $V_{DD}$ ) lorsque la tension  $U_{MH}$  aux bornes du condensateur atteindra la valeur de basculement des portes  $V_{DD}/2$ .

2em cas

$$V_{s} = 0V \text{ et } V_{H} = V_{DD} \tag{I.34}$$

On a donc

$$U_{SH} = -V_{DD} \tag{I.35}$$

Dans ce cas, le condensateur se charge vers la tension  $-V_{DD}$  ( $V_M$  diminue), et la première porte basculera ( $V_s$  passera à $V_{DD}$ ) lorsque  $V_M$  atteindra $V_{DD}/2$ . Mais quelle sera la valeur de  $U_{MH}$  aux bornes du condensateur lorsque  $V_M$  vaudra  $V_{DD}/2$ .

On peut conclure alors que  $V_S$  basculera à  $V_{DD}$  (et  $V_H$  à 0V) lorsque la tension  $U_{MH}$  aux bornes du condensateur atteindra la valeur de basculement  $-V_{DD}/2$ .

#### > Remarque

Toute variation brutale de potentiel sur l'une des armatures d'un condensateur tel que la variation de la tension  $U_{SH}$  est instantanément et intégralement reportée sur l'autre armature. Cela veut dire, dans le cas de notre montage astable, que si la tension  $V_H$  à la sortie de la seconde porte logique passe, par exemple, de 0V à  $+V_{DD}$  instantanément, le potentiel au point M est augmentée aussi instantanément d'une valeur égale à $V_{DD}$ . Il en résulte alors à des pics de tension à 3.  $V_{DD}/2$  sur le chronogramme du signal $V_M$ .

On peut alors calculer la période du signal de sortie obtenu. Dans l'astable à 2 portes logiques inverseuses, les temps  $t_H$  et  $t_B$  sont égaux, et correspondent au temps que met le condensateur pour se charger de  $-V_{DD}/2$  à  $+V_{DD}/2$ , la tension d'alimentation du circuit de charge étant égale à  $V_{DD}$ ». On en déduit que :

Le rapport cyclique d=0,5 ( $V_s$  est un signal carré).

$$t_H = t_R = R.C.Ln(3) 1,1.R.C$$

(I.36)

La période du signal de sortie  $V_S$  est donc :

$$T = 2.R.C.Ln(3)$$

(I.37)

#### 3. Filtres électronique

#### 3.1. Définition

Un filtre est un circuit électronique qui réalise une opération de traitement du signal. Autrement dit, il atténue certaines composantes d'un signal et en laisse passer d'autres.

Il existe plusieurs types de filtres, dont les plus connus sont :

- filtre passe-haut

- filtre passe-bas

- filtre passe-bande

#### 3.2. Types de filtres

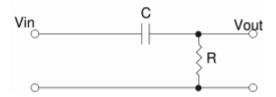

#### > filtre passe-haut

Le concept de filtre passe-haut est d'atténuer les fréquences inférieure à sa fréquence de coupure  $f_c$  et ce, dans le but de conserver uniquement les hautes fréquences.

La fréquence de coupure du filtre est la fréquence séparant les deux modes de fonctionnement idéaux du filtre: bloquant ou passant.

L'expression du gain de ce filtre passe haut sera exprimé par:

$$AV = \frac{V_{out}}{V_{in}} = \frac{jRC\omega}{1 + jRC\omega} \tag{I.38}$$

Figure I.15: Filtre passe-haut du premier ordre [3].

## > Filtre passe-bas

Le concept de filtre passe-bas est d'atténuer les fréquences supérieures à sa fréquence de coupure f<sub>c</sub> et ce, dans le but de conserver uniquement les basses fréquences. La fréquence de coupure du filtre est la fréquence séparant les deux modes de fonctionnement idéaux du filtre: passant ou bloquant.

La formule :

$$AV = \frac{V_{out}}{V_{in}} = \frac{1}{1 + jRC\omega}$$

(I.39)

Figure I.16: Filtre passe-bas du premier ordre [3].

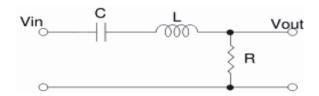

#### > Filtre passe-bande

Un filtre passe-bande est un filtre ne laissant passer qu'un intervalle de fréquences celui-ci étant limité par la fréquence de coupure basse et la fréquence de coupure haute du filtre.

Les applications en électronique sont multiples. Un circuit passebande peut servir à éliminer le bruit du signal, si l'on sait que le signal a des fréquences comprises dans une gamme de fréquences déterminée. C'est aussi un circuit passe-bande qui permet, en radiocommunication, de sélectionner la fréquence radio écoutée.

Figure I.17: Filtre passe-bande [3].

#### Remarque

Parmi les types de filtres cités au-dessus, nous sommes intéressés par le type de filtre passe bas dans notre travail.

#### 4. Trigger de Schmitt

Une bascule de Schmitt, aussi appelée trigger de Schmitt ou bascule à seuil, est un circuit logique inventé en 1934 par Otto Schmitt

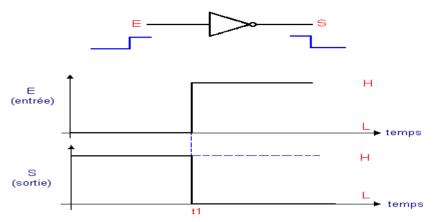

Figure I.18: signaux réel à l'entrée et à la sortie de l'inverseur [4].

#### 4.1. Fonctionnement

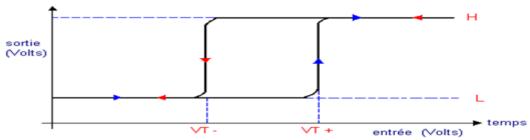

Ce sont les bascules de Schmitt ou encore triggers de Schmitt. L'idée fondamentale est de créer deux seuils de basculement, l'un sur le front montant d'un signal, l'autre sur le front descendant de ce signal. Ceci est représenté à la figure I.19.

Figure I.19 : Signaux à l'entrée et à la sortie d'un trigger de schmitt [4].

A l'instant t1, la tension présente à l'entrée atteint le seuil de basculement VT+, la sortie passe très rapidement du niveau logique L au niveau logique H, bien que le seuil VT+ soit franchi plusieurs fois au cours des oscillations présentes à l'entrée du trigger.

Au cours du front descendant, c'est à l'instant t2 que le signal d'entrée franchit le seuil de basculement VT- . La sortie passe alors très rapidement du niveau logique H au niveau logique L.

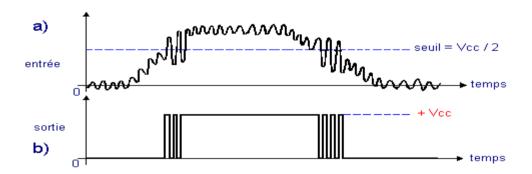

Les deux instants de basculement sont les deux instants où le signal franchit pour la première fois le seuil considéré. Il est évident que plus la différence (VT+) - (VT-) est importante, plus ce circuit sera fiable et insensible aux fluctuations parasites superposées au signal originel. Cet écart de tension entre les deux seuils est appelé hystérésis. C'est une caractéristique propre à un trigger de Schmitt. Le cycle d'hystérésis est représenté à la figure I.20.

Figure I.20: Cycle d'hystérésis d'une bascule de schmitt [4].

#### 5. Le transistor bipolaire

#### 5.1. Constitution

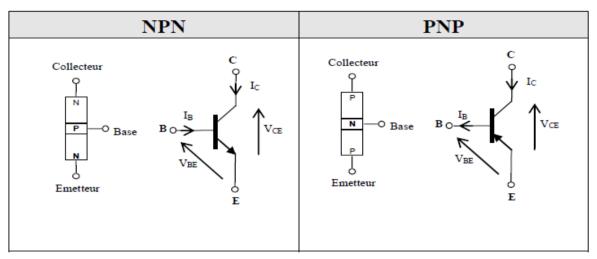

Un transistor bipolaire est constitué par un cristal semi-conducteur (Germanium ou silicium) comportant trois zones dopées différemment de façon à former :

- Soit de 2 zones dopées N (phosphore, arsenic, antimoine) séparées par une zone dopée P (bore, gallium, indium), c'est le transistor NPN.

- Soit de 2 zones dopées P séparées par une zone dopée N, c'est le transistor PNP.

Figure I.21: transistor NPN et PNP [5].

## 5.2. Principe de fonctionnement

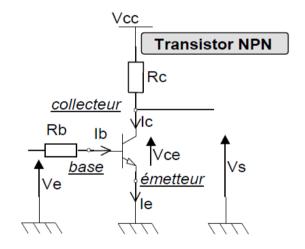

Figure I.22: transistor NPN [5].

Un courant de base Ib provoque la conduction du transistor.

#### • Relations principales :

$$Ib + Ic = Ie (I.40)$$

$$Vcc = Vce + Rc.Ic$$

(I.41)

$$Ve = Vbe + Rb.Ib (I.42)$$

$$Pdissip\acute{e} = Vce.Ic$$

(I. 43)

Selon la valeur d'Ib on distingue trois régimes de conduction :

- Blocage

- Linéaire

- Saturation

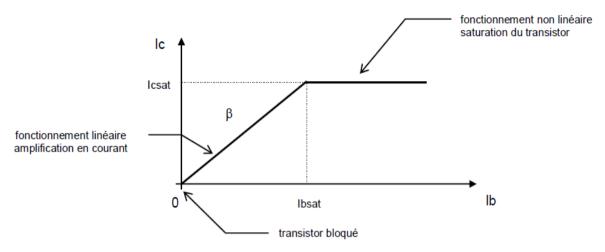

Figure I.23: régime de conduction [5].

#### 5.3. Les régimes de fonctionnement

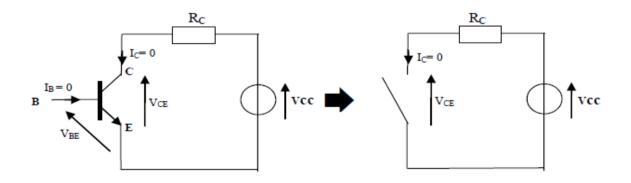

#### 5.3.1. Régime de blocage (état bloqué)

Condition : Ib = 0

Très grande résistance (quelques  $M\Omega$ ) entre Emetteur et Collecteur

Le transistor est équivalent à un interrupteur ouvert.

$$D'o\dot{u}: Ic = 0 Vce = Vcc (1.44)$$

$\triangleright$  Puissance dissipée par le transistor =  $Vcc \times Ic = 0$

Figure I.24: transistor équivalent à un interrupteur ouvert [5].

#### 5.3.2. Régime linéaire (amplificateur)

Condition: 0 < Ib < Ib sat

Le transistor se comporte comme une source de courant *Ic* proportionnelle à *Ib*.

D'où :

$$Ic = \beta x Ib$$

$0 < Vce < Vcc$

Puissance dissipée par le transistor =  $Vce x Ic = Vce x \beta x Ib$  (importante)

$\beta$  est le gain en courant du transistor. Les constructeurs indiquent les valeurs extrêmes  $\beta$  min et  $\beta$  max (dispersion de fabrication). Le coefficient d'amplification  $\beta$  est aussi désigné par  $h_{FE}$ .

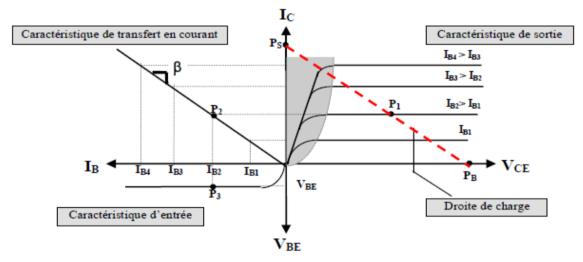

#### • Réseau de caractéristiques du transistor :

Figure I.25: caractéristiques du transistor [5].

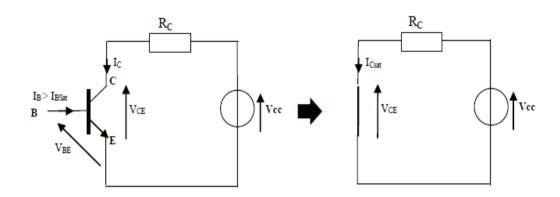

### 5.3.3. Régime de saturation (état passant)

Condition : *Ib* > *Ib* sat (**important**)

Très faible résistance (quelques $\Omega$ ) entre Emetteur et Collecteur

Le transistor est équivalent à un interrupteur fermé d'où :

$$Ic = Ic max = Ic sat (limité par Rc et Vcc) Vce = Vce sat \approx 0$$

$$I_{Csat} = \frac{V_{CE} - V_{CEsat}}{R_C} \tag{I.45}$$

## **>** Puissance dissipée par le transistor = $Vce \ sat \ x \ lc \ sat \ \approx \ 0$

#### • Calcul de Ib sat :

$Ib_{satmin} = \frac{IC_{sat}}{\beta_{min}} \rightarrow$  Dans la pratique choisi une valeur 2 à 3 fois supérieure.

Figure I.26: transistor équivalent à un interrupteur fermé [5].

#### **5.4.** Le transistor en commutation (interrupteur statique)

En régime de commutation, passage de l'état bloqué à l'état saturé et inversement, le transistor joue le rôle d'un interrupteur électronique unidirectionnel commandé par le courant de base Ib. Le transistor est équivalent, entre ses bornes collecteur et émetteur, à un interrupteur dont la commutation est commandée par le courant de base Ib. Dans ce cas, Le transistor n'utilise donc que deux régimes qui dissipent peu d'énergie.

#### 5.5. Le transistor BD139

Le BD139 est un transistor NPN basse tension complémentaire traversant dans un boîtier TO-126 (SOT-32).

Ce dispositif fabriqué en technologie planaire épitaxial Utilisé pour les amplificateurs et les Drivers audio, en utilisant des circuits complémentaires.

Figure I.27: transistor BD139 [6].

## 5.5.1. Caractéristiques électriques du transistor BD139

- ➤ Tension Collecteur-Emetteur (VCE) de 80V

- Courant collecteur (Ic) de 1.5A.

- ➤ Dissipation de puissance (Pd) de 12.5W.

- ➤ Tension de saturation Collecteur-Emetteur de 500 mV avec un courant de collecteur de 0.5A.

- ➤ Gain en courant DC (hFE) de 25 avec un courant de collecteur de 0.5A.

- ➤ Gamme de température de jonction de 150°C.

#### 5.6. Le transistor BC547

Le BC547B est un transistor silicium épitaxial NPN traversant en boîtier TO-92. Le transistor Convient pour la commutation et l'amplification.

## 5.6.1. Caractéristiques électriques du transistor BC547

- ➤ Tension de claquage Collecteur vers Emetteur de 45V

- > Tension de claquage Collecteur vers Emetteur de 250mV

- Dissipation de puissance de 500mW

- Courant de collecteur DC de 100mA

- $\triangleright$  Gain du courant DC de 110 avec Ic = 2mA

- Plage de température de jonction de -65° C à 150° C

## 5.6.2. Applications du transistor BC547

- > Traitement du Signal.

- > Gestion d'alimentation.

- Périphériques Portables.

- Electronique Grand Public.

- > Industrie

#### 6. Montage Darlington

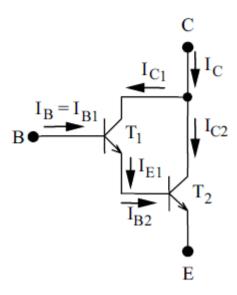

Après avoir présenté brièvement les transistors bipolaires, on présente alors le montage Darlington conçu à partir de deux transistors bipolaires de même type et utilisé principalement comme amplificateur de courant. C'est ainsi qu'afin de commander de forts courants, généralement supérieurs 1A, à partir d'un circuit électronique qui ne peut pas débiter un fort courant, il est nécessaire de disposer de transistor avec un coefficient d'amplification supérieur à 1000. Pour cela on associe deux transistors de même type. C'est le cas du montage Darlington. On peut toutefois remarquer qu'il existe deux types de montage Darlington soit alors: le montage Darlington à transistors NPN et le montage Darlington à transistors PNP. On présente dans ce travail le montage Darlington à transistors NPN que nous avons utilisé dans notre étude.

### 6.1. Principe

Comme nous l'avons déjà cité auparavant, le montage Darlington est constitué par l'association de deux transistors T1 et T2 de même Type (deux **PNP** ou deux **NPN**). T2 est un transistor de puissance donc de gain en courant petit et dont l'impédance d'entrée h'11 pour le courant nominal est faible ; T1 est un transistor d'usage général de gain normal. La base du transistor T2 est reliée à l'émetteur de T1 et les deux collecteurs sont reliés.

L'ensemble est un dispositif à trois électrodes équivalent à un transistor unique dont on va déterminer les paramètres.

Figure I.28: Montage Darlington [7].

Le courant de base  $I_B$  du transistor T1 est amplifié successivement par le transistor T1 puis par le transistor T2. Ce montage est assimilable à un « super transistor » dont le coefficient d'amplification total  $\beta$  est très élevé car il correspond au coefficient d'amplification  $\beta_1$  du premier transistor multiplié par le coefficient d'amplification  $\beta_2$  du second transistor.

Coefficient d'amplification total du montage

$$\beta = I_C/I_B = \beta_1 \mathbf{x} \beta_2$$

(I. 46)

#### • Calcul du gain en courant :

En continu, le courant qui circule dans le collecteur est donné par:

$$I_C = \beta_2 I_{B2} \tag{I.47}$$

Or,

$$I_{B2} = I_{E1} = I_{C1} + I_{B1} = \beta_1 I_{B1} + I_{B1}$$

(I. 48)

On déduit :

$$I_C = \beta_2 I_{B2} = \beta_2 (\beta_1 + 1) I_{B1} \approx \beta_1 \beta_2 I_{B1} = \beta_1 \beta_2 I_B$$

(I.49)

Le gain en courant est donc :

$$\beta \approx \beta_1 \beta_2$$

(I.50)

Le gain statique en courant du transistor équivalent est approximativement égal au produit des gains statiques en courant des deux transistors. Ce gain en courant reste valable pour l'alternatif. La différence de potentiel entre la base et l'émetteur est :  $V_{BE} = V_{BE1} + V_{BE2}$

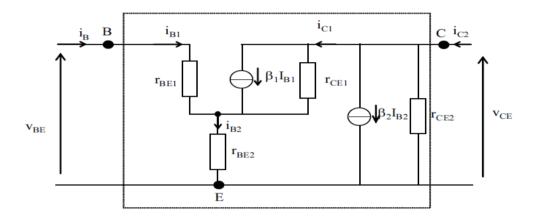

#### 6.2. Schéma équivalent en petits signaux

Le schéma équivalent dynamique du montage en petits signaux et en basses fréquences est présenté figure I.29.

Figure I.29: Schéma équivalent du transistor Darlington en régime petits signaux [7].

#### 6.3. Paramètres du circuit

#### 6.3.1. Résistance d'entrée

La résistance d'entrée  $r_{BE}$  du transistor équivalent constitué des deux NPN peut être trouvée à partir du schéma équivalent du montage en régime petits signaux.

$$r_{BE} = \frac{v_{BE}}{i_B} \left| V_{CE=0} \right| \tag{I.51}$$

$$i_{B2} = i_{B1} + \beta_1 i_{B1} + \frac{v_{CE} - i_{B2} r_{BE2}}{r_{CE1}}$$

(I.52)

Quand  $V_{CE} = 0$ , sachant que  $r_{BE2}$ \_ $r_{CE1}$ , le courant  $i_{B2}$ devient :

$$i_{B2} = i_{B1} + \beta_1 i_{B1} - \frac{r_{BE2}}{r_{CE1}} i_{B2} \approx i_{B1} + \beta_1 i_{B1} \approx \beta_1 i_{B1}$$

(I.53)

et:

$$r_{BE} = \frac{v_{BE}}{i_B} = \frac{r_{B1}i_B + \beta_1 r_{BE2}i_B}{i_B} = r_{B1} + \beta_1 r_{BE2}$$

(I.54)

On remarque alors que Cette résistance est bien plus élevée que la résistance d'un seul transistor.

#### 6.3.2. Résistance de sortie

La résistance de sortie du montage est telle que:

$$r_{CE} = \frac{v_{CE}}{i_C} \Big| i_B = 0 \tag{I.55}$$

Or, quand  $i_B = 0$ , le schéma équivalent du montage devient :

Figure I.30: Schéma équivalent simplifié permettant de déterminer la résistance de sortie [7].

Le courant Ic a pour expression:

$$i_C = \beta_2 i_{B2} + \frac{v_{CE}}{r_{CE2}}$$

,  $i_{B2} = \frac{v_{CE}}{r_{BE2} + r_{CE1}}$  (I.55)

L'expression de la résistance de sortie du montage devient:

$$r_{CE} = \frac{1}{\frac{1+\beta_2}{r_{CE1}+r_{BE2}} + \frac{1}{r_{CE2}}} \approx \frac{1}{\frac{\beta_2}{r_{CE1}} + \frac{1}{r_{CE2}}}$$

(I.56)

On remarque alors que la résistance de sortie du montage est inférieure à la résistance de sortie du deuxième transistor et très inférieure à celle du premier transistor.

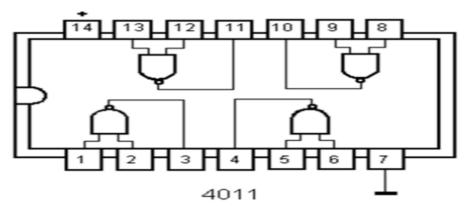

#### 7. Circuit intégré CD 4011

Le CD 4011 est un circuit intégré à 14 pins en DIL (Dual In Line Package), composé De 4 portes logique NAND.

#### 7.1. Caractéristiques

- Courant de repos déterminés jusqu'à 20A

- 5V, 10V et 15V : notations paramétriques

- Fuite de courant d'entrée = 100na (max) et VDD =18V à T = 25°C

- 100% test de courant de repos

- Respecte toutes les exigences des normes pour les descriptions de la série des dispositifs CMOS.

•

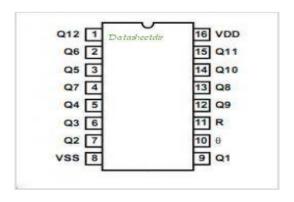

## 8. Compteur binaire CD4040

Le CD 4040 est un circuit intégré à 16 pins.

## 8.1. Caractéristiques

• tension d'alimentation: 3.0V à 15V

• Haute immunité au bruit: 0,45 VDD

- Compatibilité TTL de puissance faible

- fonctionnement à vitesse moyenne: 8 MHz. à VDD = 10V

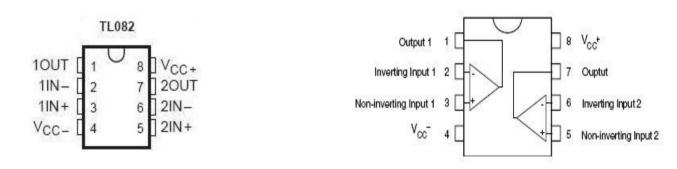

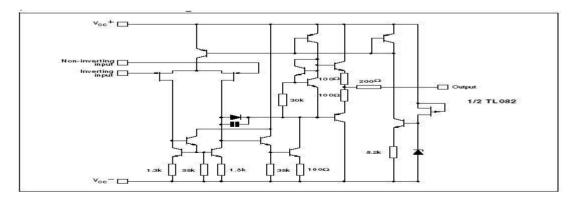

Après avoir présenté le générateur aléatoire numérique et ses constituants, on présente dans ce second chapitre le générateur analogique.

#### Il se compose de :

- Alimentation 15V

- Amplificateur TL082

- Les montages d'amplificateur

- Transistor de type 2N2222

- Potentiomètre (Resistance variable)

Nous allons dans ce qui suit présenté tous les éléments de ce générateur analogique :

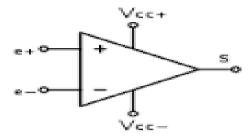

#### 1. L'AMPLIFICATEUR OPERATIONNEL

#### 1.1. Généralités

Les amplificateurs opérationnels appelés aussi " op amp" ou "AO" ont été au départ inventés pour résoudre analogiquement les problèmes numériques, on citera entre autre l'étude des équations différentiels dont les solutions analytiques sont inconnues. Notons toutefois que les amplificateurs opérationnels ont été au départ conçus avec des composants discrets, avec les progrès technologiques incessants, l'électronique intégrés a permis alors la conception d'amplificateurs opérationnels ayants d'excellentes performances et avec des couts très compétitifs. Ces derniers ne nécessitent alors que peu de composants périphériques, éliminant par la même occasion les problèmes délicats de polarisation engendrés par les AO réalisés avec des composants discrets. Globalement, les amplificateurs opérationnels sont largement utilisés dans de nombreux domaines de l'électronique analogique.

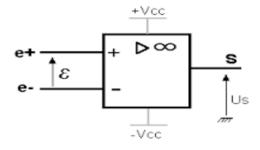

## 1.2. Représentations symboliques de l'amplificateur opérationnel

Dans tous les schémas électroniques, on représente l'ampli-op par un symbole graphique. On peut utiliser indifféremment l'un des ces schémas des figures suivantes.

## \* symbole américain :

Figure II.1: Symbole européen de l'amplificateur opérationnel [10].

## \* symbole européen :

Figure II.2: Symbole américain de l'amplificateur opérationnel [10].

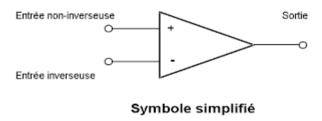

## \*symbole simplifié:

Figure II.3: Symbole simplifié de l'amplificateur opérationnel [10].

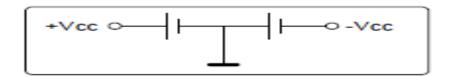

#### 1.3. Polarisation de l'amplificateur opérationnel

Figure II.4: Polarisation de l'amplificateur opérationnel [10].

Pour éviter l'emploi de condensateurs de liaison entre étages, on polarise l'AOP avec deux sources de tension +Vcc -Vcc généralement symétriques, leur point milieu étant relié à la masse du montage (l'AOP ne possède pas de borne de masse). L'absence de condensateurs de liaison autorise l'amplification de tensions continues. Si on ne dispose pas d'alimentation symétrique, on peut polariser l'AOP avec un pont de résistances, mais il sera alors nécessaire d'ajouter des condensateurs de liaison. Afin d'éviter l'entrée en oscillations d'un montage à AOP, il est nécessaire de découpler les alimentations avec des condensateurs. Généralement un condensateur de 100 nF entre chaque broche d'alimentation (le plus près possible du circuit intégré) et la masse.

#### 1.4. Caractéristiques

Après avoir présenté brièvement les caractéristiques des AOP, on les présente dans ce qui suit avec plus de détails.

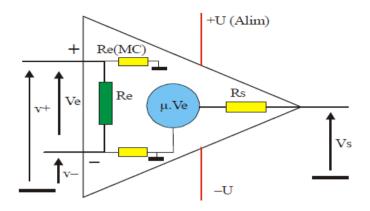

#### 1.4.1. L'impédances d'entrée, de sortie et gain en puissance

Considérons le schéma interne de l'AO, ou sont représentés l'impédance d'entrée, de sortie et le gain de ce composant.

Figure II.5: schéma interne de l'AOP [10].

#### 1.4.2. Impédance d'entrée

L'impédance d'entrée Ze correspond au courant d'entrée. Elle peut être représentée comme une résistance branchée entre les deux entrées de l'AOP. C'est cette impédance qui consomme de la puissance sur l'élément connecté à l'entrée. Or avec les AO, cette impédance est très élevée, le courant d'entrée est très faible, inférieur à 200nA pour les AO les moins. Cette qualité est très importante car elle permet de ne pas perturber la source connectée à l'entrée, ce qui est particulièrement utile lorsque l'on souhaite réaliser des mesures.

## 1.4.3. Impédance de sortie

L'impédance de sortie Zs s'apparente à la résistance interne d'un générateur. On peut la représenter comme une résistance en série avec la charge branchée à la sortie, et forme alors avec celle-ci un diviseur de tension, diminuant le gain en tension de l'AO, d'autant plus qu'elle est élevée, et cette impédance de sortie avec les AO est très faible, de l'ordre de quelques ohms. C'est également une très grande qualité puisque cela rend la tension de sortie quasiment indépendante de la charge branchée sur la sortie.

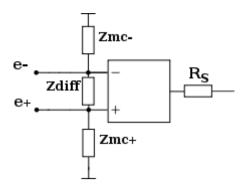

Figure II.6: Modélisation d'un AOP comprenant les impédances d'entrées et de sortie [10].

#### 1.4.4. Gain en puissance

Ces notions d'impédance sont en fait étroitement liées au gain en puissance de l'AO, c'est à dire le rapport entre la puissance de sortie et la puissance d'entrée.

Comme vous le savez, la puissance est définie par  $P=U\times I$ Le gain en puissance est donc:

$$G_p = \frac{P_s}{P_e} = \frac{U_S I_S}{U_e I_e} \tag{II.1}$$

Puisque Ie est faible Pe l'est également, et puisque Rs est très faible Is est plus importante et Ps aussi, donc le gain en puissance est très important, ce qui est une grande qualité de l'AO.

### 1.5. Tension de décalage et courants d'entrée

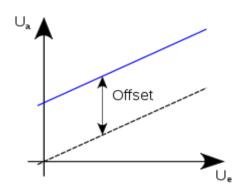

Lorsqu'un amplificateur opérationnel ne reçoit aucun signal sur ses entrées (lorsque ses entrées sont toutes les deux réunies à zéro), il subsiste généralement une tension continue de décalage de la tension de sortie vis-à-vis de zéro. Ce décalage (ou *offset*) provient de deux phénomènes : la tension de décalage propre aux circuits internes de l'AOP d'une part, et l'influence des courants de polarisation de la paire différentielle des transistors d'entrée sur le circuit

extérieur d'autre part. La tension de décalage représente la différence de tension qu'il faudrait appliquer entre les deux entrées d'un AOP en boucle ouverte, quand on a relié une des entrées au zéro, pour avoir une tension de sortie nulle. Cette tension d'offset peut être représentée en série avec l'entrée non-inverseuse ou inverseuse.

Figure II.7: Conséquence de l'offset (Ua=Vs) [10].

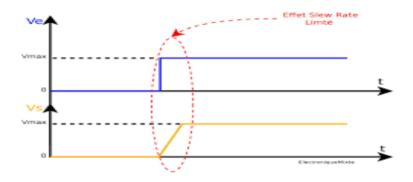

#### 1.6. Vitesse de balayage

La vitesse de balayage (ou *slew rate*) représente la vitesse de variation maximale de tension ue peut produire un amplificateur. Lorsque la vitesse de variation du signal de sortie d'un amplificateur est supérieure à sa vitesse de balayage, sa tension de sortie est une droite

$$SR = max \left(\frac{dv_s(t)}{dt}\right) \tag{II.2}$$

La vitesse de balayage est exprimée en V/µs.

Dans un AOP, le *slew-rate* dépend généralement du courant maximum que peut fournir l'étage différentiel. L'étage différentiel fournit à l'étage d'amplification de tension un courant proportionnel à la différence de tension entre les deux entrées. Ce courant sert majoritairement à charger la capacité de compensation interne C présente dans l'étage d'amplification en tension. La relation courant / tension est alors celle d'un condensateur :

$$i = c \frac{dV_c}{dt} \tag{II.3}$$

Le courant maximum que peut fournir l'étage d'entrée étant égal à deux fois le courant de polarisation **Ico**traversant le collecteur d'un des transistors d'entrée, le *slew-rate* peut s'obtenir de la façon suivante :

$$SR = \frac{2I_{c0}}{C} \tag{II.4}$$

Figure II.8: effet du slew-rate [10].

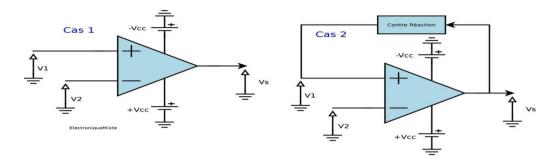

## 1.7. Réaction positive et contre-réaction

#### 1.7.1. Définitions :

On dit qu'il y a **réaction positive** quand la sortie est reliée à l'entrée non inverseuse (+) Cas (2).

On dit qu'il y a **contre-réaction** (ou réaction négative) quand la sortie est reliée à l'entrée inverseuse(-) Cas (1)

L'entrée notée (+) est appelée : entrée non inverseuse

L'entrée notée (-) est appelée : entrée inverseuse

Figure II.9: Réaction positive et contre-réaction [10].

## 1.8. Application

L'AOP est un composant très présent dans les montages analogiques :

- réalisation de filtre actif : les filtres à base d'AOP permettent d'atteindre des précisions plus importantes que des filtres passifs.

- amplification de signaux : l'AOP est à la base de nombreux schémas permettant le conditionnement des capteurs, on parle alors du domaine d'instrumentation.

- réalisation de calculs analogiques : malgré les progrès du traitement numérique, l'AOP reste utilisé pour réaliser des calculs analogiques : addition/soustraction, gain, multiplication, intégration/dérivation. Il peut être utilisé par exemple en automatique pour réaliser des asservissements, des régulateurs PID, etc.

## 2. Montages de base de l'amplificateur opérationnel

## 2.1. Amplificateur suiveur de tension

## a) schéma

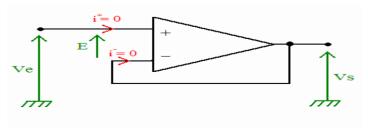

Figure II.10: amplificateur suiveur de tension [11].

## **b**) La sortie de cet étage s'exprime par:

$$V_{s} = V_{e} \tag{II.5}$$

#### c) Remarques

La résistance en entrée du montage est infinie. Le suiveur de tension permet de prélever une tension sans la perturber, car il possède un courant d'entrée nul. On le rencontre donc régulièrement lors de la présence de sonde.