- [1] Réseau Telecom network, "3G: La course est lance ", vol. 50, no. 6 Novembre 2011.

- [2] C. Majek, "Contribution a l'étude d'un synthétiseur de fréquence pour objets communicants multistandards en technologie CMOS SOI", *Thèse de Doctorat*, Université Bordeaux, Octobre 2006.

- [3] K. Ibrahimi, "Gestion des ressources des réseaux mobiles de nouvelle génération par rapport à la mobilité des utilisateurs", *Thèse de Doctorat*, Université d'Avignon, 2009.

- [4] M. King Tcheumtchoua Kamdem, "Conception et simulation d'un brouilleur GSM", Master Recherche, Ecole Nationale Supérieure Polytechnique 2010.

- [5] M. Olivier, "Conception de synthèses de fréquences à 24 GHz à base de diviseurs à mémoires D en technologies silicium avancées ", *Thèse de Doctorat*, Université Bordeaux 1 Décembre 2008.

- [6] J. Cellmer, "Réseaux cellulaires, Système UMTS", Ingénieur des télécommunications Chef de département télécommunication, Réseaux ferré de France, *Techniques de l'ingénieur-TE7368*-, Mai 2002.

- [7] M. Terré, "UMTS Eléments d'analyse de la couche physique", support de cours version 5.0; Ecole Nationale Supérieure des Télécommunication de Bretagne.

- [8] J. Mukherjee, P. Roblin, & S.Akhtar, "An Analytic Circuit-Based Model for White and Flicker Phase Noise in LC Oscillators", *IEEE Transactions on Circuits and Systems—I:* Regular Papers, vol. 54, no. 7, pp. 1584 1598, July 2007.

- [9] P. Olivier Lucas, "Conception orientée délai : étude, développement et réalisation d'une boucle à verrouillage de phase large bande stabilisée par une boucle à verrouillage de délai", *Thèse de Doctorat*, Université Bordeaux ,11 Mais 2011.

- [10] D. Rouffet, S. kerboeuf, L. Cai & V. Capdevielle, "4G Mobile", *Alcatel, Technical Paper*, 2005.

- [11] J-S. Hwang, R. Consulta & H-Y Yoon, "4G Mobile Networks Technology Beyond 2.5G and 3G", PTC (Pacific Telecommunications Council) Proceedings, Hawaii, 2007.

- [12] J. Blin & S. Renault, "4G, la convergence ultime", Article rédigé dans www.01net.com, 2004.

- [13] A.H. Khan, M.A. Qadeer, J.A. Ansari and S. Waheed, "4G as a Next Generation Wireless Network", *Future Computer and Communication. ICFCC 2009*. pp 334 338, Avril 2009.

- [14] B. Krenik,"4G wireless technology: When will it happen? What does it offer? ", Solid-State *Circuits Conference*, 2008. A-SSCC '08. IEEE Asian, pp 141 144, Novembre 2008.

- [15] D.Christian, "La Convergence se jouera entre WiMAX, LTE et UMB", In-Stat, *Article rédigé dans www.generation-nt.com*, 2007.

- [16] M-A. Delalande, "L'ITU reconnaît officiellement WiMAX comme une technologie 3G", *Article rédigé dans www.reseaux-telecoms.net*, 2007.

- [17] IEEE Std, "Air Interface for Fixed Boradband Wireless Access Systems", *Local and Metropolitan Area Networks*, Part 16, 2004.

- [18] H.Wang, L. Kondi, A. Luthra, S. Ci, "4G Wireless Video Communications", Wiley Series on Wireless Communications and Mobile Computing, ISBN: 978-0-470-77307-9 Hardcover. Livre, Avril 2009.

- [19] Motorola, "Long Term Evolution (LTE): A Technical Overview ", *Technical White Paper*, 2007.

- [20] G. Fritze, "SAE The Core Network for LTE", Ericsson, Technical white paper, 2008.

- [21] U.Barth, "3GPP Long-Term Evolution / System Architecture Evolution Overview", *Alcatel, Technical white paper,* Septembre 2006.

- [22] A.Larmo et al, "The LTE link-layer design", *Communications Magazine, IEEE*, Vol.47, No 4, pp. 52–59, Avril 2009.

- [23] Man Hung Ng; Shen-De Lin; Li, J.; Tatesh, S., "Coexistence studies for 3GPP LTE with other mobile systems", *Communications Magazine, IEEE*, Vol.47, No 4, pp. 60–65, Avril 2009.

- [24] A. Hajimiri, Lee T. H. " A General Theory of Phase Noise in Electrical Oscillators", IEEE Journal of Solid-State Circuits, Vol.33, no. 2, février 1998.

- [25] B. Razavi, " A study of phase noise in CMOS oscillators " *IEEE Journal of Solid-State Circuits*, Vol.31, no. 3, mars 1996.

- [26] J-A.McNeil, "Jitter in ring oscillators ", *Thèse de doctorat*, University of Boston, College of Engineering, chapitre 1, 1994.

- [27] M.Sié, "Synthétiseurs de fréquence monolithiques micro-ondes à 10 et 20 GHz en technologies BiCMOS SiGe 0,25 et 0,35 µm", *thèse de Doctorat* de l'Université Paul Sabatier de Toulouse, 2004.

- [28] V.Cheynet, "Dispositifs à Faible Coût Appliqués à la Synthèse de Fréquences et à la Modulation FSK pour les Systèmes de Radiocommunication", *Thèse Doctorat* de l'université d'Aix Marseille 1 Mention Physique et Modélisation des systèmes complexes, 15 juin 2009.

- [29] M.Perrott, "Techniques for High Data Rate Modulation and Low Power Operation of Fractional-N Frequency Synthesizer ".*Chapitre 1: Introduction, Thèse, Massachusetts* Institute of Technology, 1997.

- [30] S-J. Lee, B. Kim and K. Lee, "A Fully Integrated Low-Noise 1-GHz Frequency Synthesizer Design for Mobile Communication Application", *IEEE Journal of Solid-State Circuits*, Vol. 32, No. 5, May 1997, pp. 760-765.

- [31] William O. Keese, "An Analysis and Performance Evaluation of a Passive Filter Design Technique for Charge-pump PLL's", *National Semiconductor Application Note*, AN-1001, July 2001.

- [32] Floyd M. Gardner, "Charge-pump phase-lock loops", *IEEE Transactions on Communications*, Vol. COM-28, No. 11, Nov. 1980, pp. 1849-1858.

- [33] D. Banarjee, "PLL Performance, Simulation, and Design", Forth Edition, 2006.

- [34] S. Kameche, M. Feham and M. Kameche, "Simulating and Designing a PLL Frequency Synthesizer for GSM Communications", *High Frequency Electronics*, Vol. 7, No.12, pp. 36-41, December 2008, *USA*..

- [35] S. Kameche, M. Feham and M. Kameche, "PLL Synthesizer Tunes DCS1800 Band", *Microwave & RF*, Vol. 46, No.6, pp. 84-90, June 2007, *USA*.

- [36] S. Kameche and M. Feham, "Perfect A PLL LTE Synthesizer", *Microwave & RF*, Vol. 51, No.1, pp. 54-66, January 2012, *USA*.

- [37] L. Lascari, "Accurate Phase Noise Prediction in PLL Synthesizers", *Applied Microwave and Wireless*, Vol. 12, No. 2, pp. 30-38, 2000.

- [38] Kyoohyun Lim and al, "A Low-Noise Phase-Locked Loop Design by Loop Bandwidth Optimization", *IEEE Journal of Solid-State Circuits*, Vol. 35, No. 6, June 2000, pp. 807-815.

- [39] Analog Devices, "PLL Frequency Synthesizer", Data Sheet ADF4106, <u>www.analog.com</u>, 2011.

# Liste des Tableaux

| Γableau I.1. Allocation de fréquences pour le LTE, a) les bandes TDD, b) les bandes FDD | 17 |

|-----------------------------------------------------------------------------------------|----|

| Tableau I.2. L'évolution des standards de radiocommunication                            | 18 |

| Tableau IV.1. Valeurs du filtre de boucle du troisième ordre                            | 54 |

# **Liste des Figures**

# **Chapitre I**

| Figure I.1. Architecture du réseau GSM                                                                                                                                                                                                                       |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                                                                              | 7  |

| Figure I.2. Liaison montante et descendante du GSM                                                                                                                                                                                                           | 7  |

| Figure I.3. Structure d'une trame de GSM                                                                                                                                                                                                                     | 8  |

| Figure I.4. Architecture du réseau UMTS                                                                                                                                                                                                                      | 10 |

| Figure I.5. Utilisation de la Bande de Fréquences pour l'UMTS                                                                                                                                                                                                | 11 |

| Figure I.6. Structure de trame de l'UMTS                                                                                                                                                                                                                     | 11 |

| Figure I.7. Techniques d'interface radio pour le GSM et l'UMTS                                                                                                                                                                                               | 12 |

| Figure I.8. L'évolution du standard LTE.                                                                                                                                                                                                                     | 14 |

| Figure I.9. Réseaux LTE commerciaux et déclarations d'intention pour le LTE                                                                                                                                                                                  | 15 |

| Figure I.10. Architecture du LTE.                                                                                                                                                                                                                            | 15 |

| Figure I.11. Structure générique de trame LTE                                                                                                                                                                                                                | 18 |

|                                                                                                                                                                                                                                                              |    |

|                                                                                                                                                                                                                                                              |    |

| Figure II.1. Illustrations des standards de communication dans la bande 0,8-10 GHz                                                                                                                                                                           | 21 |

| · ·                                                                                                                                                                                                                                                          |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 | 22 |

| · ·                                                                                                                                                                                                                                                          | 22 |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF  Figure II.3 Plage de fréquences et pas de synthèse  Figure II.4. Synthétiseur et pas de fréquences  Figure II.5. Exemple de basculement du synthétiseur entre trois fréquences |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF                                                                                                                                                                                 |    |

| Figure II.14. Schéma-bloc d'une boucle à verrouillage de phase                        | 31             |

|---------------------------------------------------------------------------------------|----------------|

| Figure II.15. Schéma-bloc d'une PLL fractionnaire                                     |                |

| Figure II.16. Diviseur de fréquences fractionnaire                                    |                |

| Figure II.17. Modulateur ∑ Δ d'ordre 2                                                |                |

| Figure II.18. Comparateur de phase et sa pompe de charge                              |                |

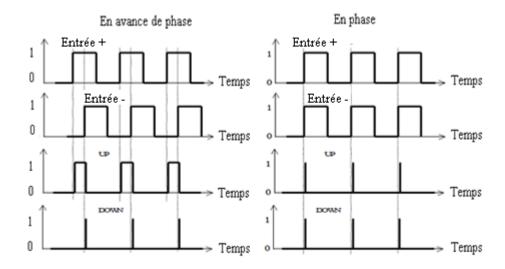

| Figure II.19. Entrées et sortie du comparateur phase-fréquence                        | 35             |

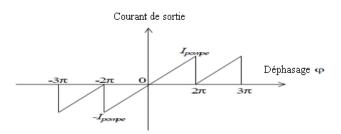

| Figure II.20. Fonction de transfert du PFD                                            | 35             |

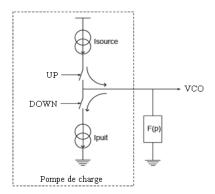

| Figure II.21. Schéma de fonctionnement de la pompe de charge associé au filtre F      | <i>E</i> (p)36 |

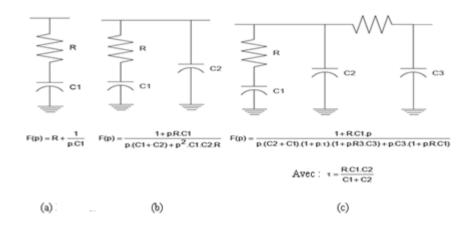

| Figure II.22. Filtres de boucle : (a) d'ordre 1, (b) d'ordre 2, (c) d'ordre 3         | 36             |

| Figure II.23. Schéma de fonctionnement du diviseur programmable par M                 | 37             |

|                                                                                       | Chapitre III   |

|                                                                                       |                |

| Figure III.1. Boucle à verrouillage de phase à base de la pompe de charge             | 40             |

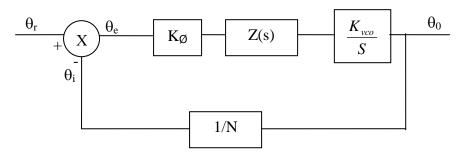

| Figure III.2 Modèle linéaire de la PLL                                                | 41             |

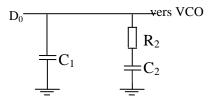

| Figure III.3. Filtre de deuxième ordre                                                | 42             |

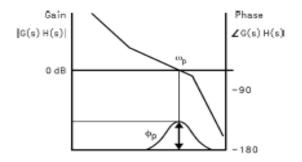

| Figure III.4. Tracé de Bode de la réponse de boucle ouverte                           | 43             |

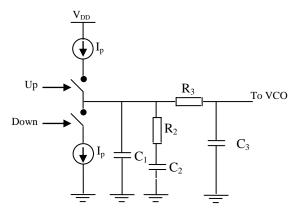

| Figure II.5. Filtre de boucle de troisième ordre combiné avec la pompe de charge.     | 45             |

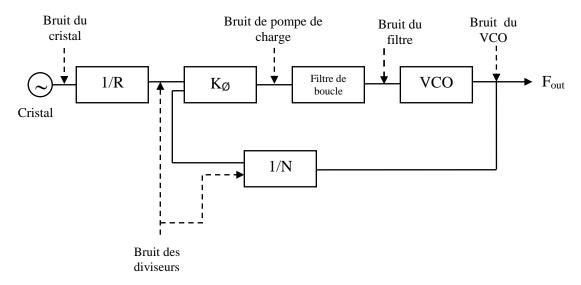

| Figure III.6. Modèle de PLL avec les différentes sources de bruits                    |                |

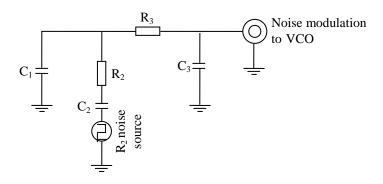

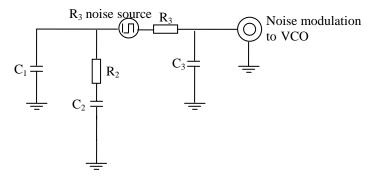

| Figure III.7. Modèle de bruit pour R <sub>2</sub>                                     | 50             |

| Figure III.8. Modèle de bruit pour R <sub>3</sub>                                     | 50             |

|                                                                                       | Chapitre IV    |

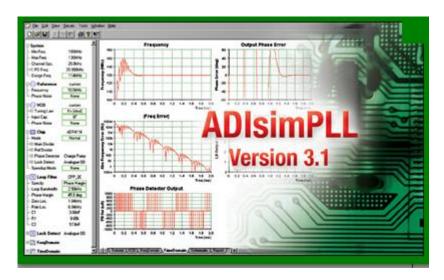

| Figure IV.1. Interface du logiciel ADIsimPLL                                          | 52             |

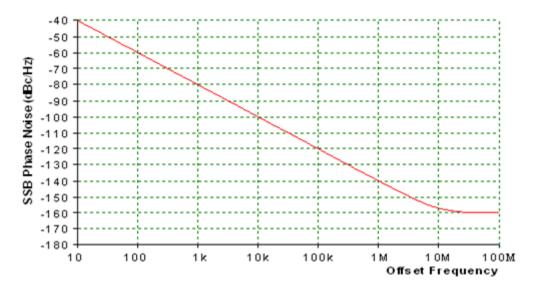

| Figure IV.2. Bruit de phase du VCO seul                                               |                |

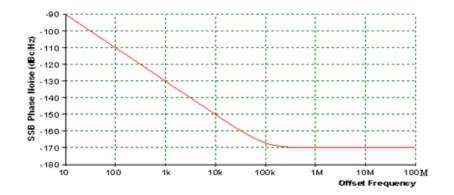

| Figure IV.3. Bruit de phase de la source de référence (TCXO)                          |                |

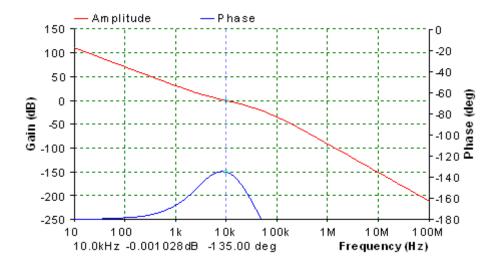

| Figure IV.4. Réponses de la boucle ouverte                                            |                |

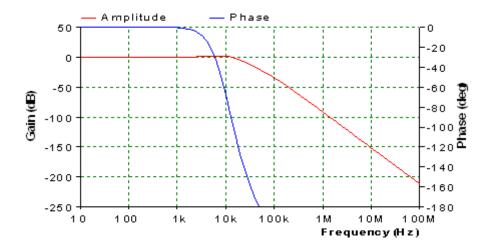

| Figure IV.5. Réponse de la boucle fermée                                              |                |

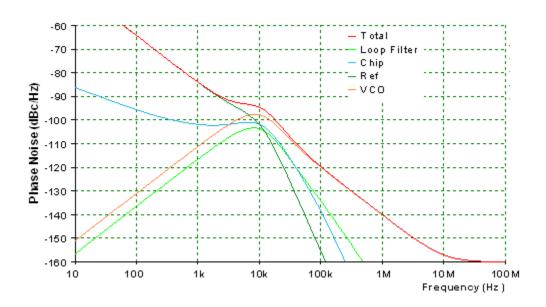

| Figure IV.6. Bruit du VCO, l'oscillateur de référence, la puce et le filtre de boucle |                |

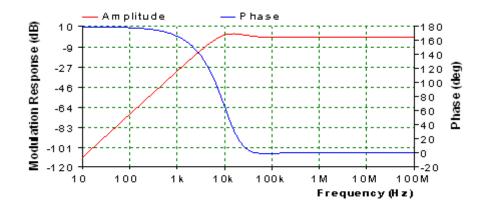

| Figure IV.7. Réponse de la modulation de fréquence                                    |                |

| Figure IV.8. Leakage spurs                                                            |                |

|                                                                                       |                |

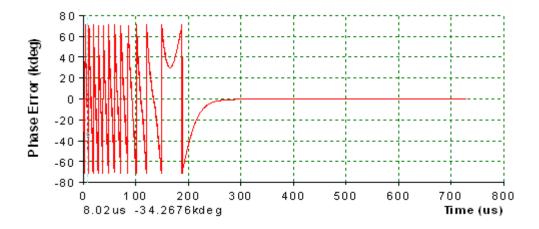

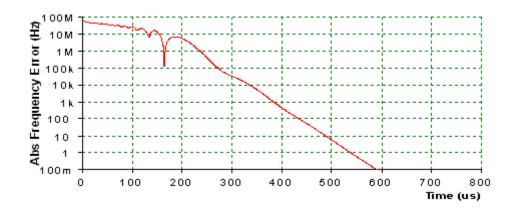

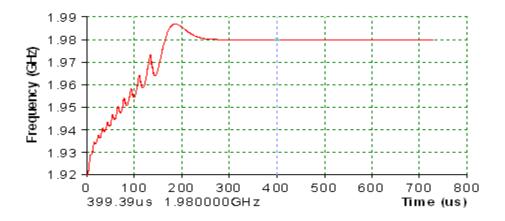

| Figure IV.9. Sortie de la pompe de charge          | 58 |

|----------------------------------------------------|----|

| Figure IV.10. L'erreur de phase à la sortie du VCO | 58 |

| Figure IV.11. L'erreur de fréquence de la PLL      | 59 |

| Figure IV 12 Réponse temporelle de la PLI          | 50 |

## Sigles et abréviations

1G 1ère Génération

2G 2ème Génération

3G 3ème Génération

3GPP 3<sup>rd</sup> Generation Partnership Project

**4G** Réseau de quatrième génération

A

AMPS Advanced Mobile Phone System

ADF Analog Devices Frequency

B

BER Bit Error Rate

BLU Bande Latérale Unique

**BB** Band de Base

C

CDMA Code Division Multiple Access

CNA Convertisseur Numérique Analogique

D

**D-AMPS** Digital Advanced Mobile Phone System

DCS Digital Communication System

**DDS** Direct Digital Synthesizer

**DS-CDMA** Direct Sequence Code Division Multiple Access

E

**EDGE** Enhanced **D**ata for **G**SM **E**volution

ETACS Extended Total Access Communication System

EPS Evolved Packet System

EPC Evolved Packet Core

## F

FDD Frequency Division Duplex

FDMA Frequency Division Multiple Access

FM Frequency ModulationFI Frequency Intermediate

G

GMSK Gaussian Minimum Shift Keying

GSM Global System for Mobile communication

GPRS Global Packet Radio Service

H

HSDPA High Speed Downlink Packet Access

HSPA High Speed Packet Access

HSUPA High Speed Uplink Packet Access

I

IEEE Institute of Electrical and Electronics Engineers

IMT-2000 International Mobile Telecommunication system 2000

ITU International Telecommunication Union

IP Internet Protocol

L

LO Local Oscillator

LTE Long Term Evolution

M

MIMO Multiple Input Multiple Output

## N

NMT Nordic Mobile Telephone

NTT Nippon Telephone and Telegraph

NADC North American Digital Cellular

0

OFDM Orthogonal Frequency Division Multiplexing

OFDMA Orthogonal Frequency Division Multiple Access

P

PCS Personal Communications Service

PDC Personal Digital Cellular

PFD Phase Frequency Detector

PLL Phase Locked Loop

PSK Phase Shift Keying

Q

QoS Quality of Service

QPSK Quadrature Phase Shift Keying

R

RF Radio Frequency

Rx Réception

S

SC-FDMA Single Carrier - Frequency Division Multiple Access

SMS Short Message Service

SSB Single Side Band

# T

TACS Total Access Communication System

TCXO Temperature Compensated Crystal Oscillator

**TDD** Time **D**ivision **D**uplex

TDMA Time Division Multiple Access

Tx Transmission

U

UMB Ultra Mobile Broadband

UIT Union Internationale des Télécommunications, en anglais ITU

UMTS Universal Mobile Telecommunication System

UTRA UMTS Terrestrial Radio Access

V

VCO Voltage Controlled Oscillator

W

W-CDMA Wideband Code Division Multiple Access

Wi-Fi Wireless Fidelity

WiMAX Worldwide Interoperability for Microwave Access

Résumé

Le réseau cellulaire a évolué très rapidement pour répondre à une demande croissante en

nombre d'utilisateurs et en débit d'information à échanger. Afin de permettre une compatibilité et

la création de nouveaux services de types multimédia et d'offrir aux usagers une itinérance à

l'échelle mondiale, il était devenu nécessaire d'effectuer un saut technologique et de franchir le pas

vers les réseaux cellulaires de 4<sup>ème</sup> génération, qui permettent l'accès simultané de plusieurs

utilisateurs à des débits élevés. Ces nouveaux services nécessitent des débits plus importants qui

sont garantis par le LTE.

Dans le domaine des télécommunications, les synthétiseurs de fréquences trouvent leurs

applications dans de nombreux dispositifs, émetteurs, récepteurs. Dans les émetteurs-récepteurs des

communications sans fil, la performance élevée d'un synthétiseur de fréquences est l'un des

paramètres important. Les boucles à verrouillage de phase (PLL) jouent un rôle majeur dans le

domaine des communications mobiles. La PLL est utilisée comme une partie essentielle du

synthétiseur de fréquences.

Le but essentiel de ce travail, consiste à la conception, la simulation et l'analyse du bruit de

phase d'un synthétiseur de fréquences à base de PLL nécessaire pour les communications mobiles

sur LTE.

Mots Clés: PLL, synthétiseur de fréquences, filtre de boucle, bruit de phase, 4G, LTE.

i

Résumé

Le réseau cellulaire a évolué très rapidement pour répondre à une demande croissante en

nombre d'utilisateurs et en débit d'information à échanger. Afin de permettre une compatibilité et

la création de nouveaux services de types multimédia et d'offrir aux usagers une itinérance à

l'échelle mondiale, il était devenu nécessaire d'effectuer un saut technologique et de franchir le pas

vers les réseaux cellulaires de 4ème génération, qui permettent l'accès simultané de plusieurs

utilisateurs à des débits élevés. Ces nouveaux services nécessitent des débits plus importants qui

sont garantis par le LTE.

Dans le domaine des télécommunications, les synthétiseurs de fréquences trouvent leurs

applications dans de nombreux dispositifs, émetteurs, récepteurs. Dans les émetteurs-récepteurs des

communications sans fil, la performance élevée d'un synthétiseur de fréquences est l'un des

paramètres important. Les boucles à verrouillage de phase (PLL) jouent un rôle majeur dans le

domaine des communications mobiles. La PLL est utilisée comme une partie essentielle du

synthétiseur de fréquences.

Le but essentiel de ce travail, consiste à la conception, la simulation et l'analyse du bruit de

phase d'un synthétiseur de fréquences à base de PLL nécessaire pour les communications mobiles

sur LTE.

Mots Clés: PLL, synthétiseur de fréquences, filtre de boucle, bruit de phase, 4G, LTE.

#### I.1. Introduction

La téléphonie mobile est un moyen de télécommunication par téléphone sans fil. Ce moyen de communication s'est largement répandu vers la fin des années 1990. Grâce à la téléphonie mobile, l'abonné a la possibilité de passer sa communication à n'importe quel endroit (en voiture, en train, à pied...) en état de mobilité ou pas.

De la fin des années soixante-dix à nos jours, plusieurs générations de standards de radiotéléphonie mobile se sont succédées. La première évolution avait pour but d'augmenter le nombre d'utilisateurs ainsi que la qualité de la voix. Les dernières générations permettent d'augmenter le débit d'informations nécessaire au développement de services multimédias (internet, vidéo...). Dans ce contexte et afin de mieux positionner ce mémoire, ce premier chapitre nous donne une brève classification des différents standards de communications mobiles.

#### I.2. De la téléphonie fixe à la téléphonie mobile

Contrairement à la téléphonie fixe qui utilise des câbles pour la liaison entre l'abonné et le réseau, la téléphonie mobile offre les services de la mobilité à un abonné. Et pour passer la communication, l'abonné a maintenant la possibilité de maintenir sa communication tout en se déplaçant. A travers les services de la mobilité, la ligne d'abonné qui relie chaque utilisateur au réseau n'est plus assurée par câbles mais plutôt par ondes radioélectriques.

La téléphonie mobile est fondée sur la radiotéléphonie, ce qui veut dire que la transmission de la voix s'effectue à l'aide d'onde radioélectrique. A cet effet, pour chaque communication, une paire de fréquences est attribuée à chaque abonné pour une communication duplex, c'est-à-dire une fréquence pour l'émission et une autre fréquence pour la réception.

#### I.3. Evolution des standards de communications mobiles

#### I.3.1. Première génération « 1G »

C'est à la fin des années 1970 et le début des années 1980 que la première génération de téléphonie mobile (notée 1G) fait son apparition. Elle possède un fonctionnement analogique et est constituée d'appareils relativement volumineux, dispendieux et à couverture limitée. De nombreux systèmes sont ainsi déployés dans le monde entier [1]:

- NMT 450 (Nordic Mobile Telephone 450MHz), crée par Ericsson, ce système utilisait des canaux de radio analogique. En 1986, Ericsson améliore ce système avec le NMT 900. Cette nouvelle version fonctionnait comme la précédente mais avec une fréquence supérieure, autour de 900MHz.

- AMPS (Advanced Mobile Phone System), apparu dans les années 80. Outre aux Etats-Unis, il en est d'usage en Russie et dans les pays Asiatique. Ce réseau analogique de première

génération possédait de faibles mécanismes de sécurité rendant possible le piratage de lignes téléphoniques.

- TACS (Total Access Communication System) constitue la version européenne du modèle AMPS. Ce système fut largement utilisé en Angleterre, puis en Asie.

- ETACS (Extended Total Access Communication System) est une version améliorée du standard TACS développé au Royaume-Uni utilisant un nombre plus important de canaux de communication.

- Radiocom 2000, apparu en France. Il utilisait des bandes de fréquences entre 167 MHz et 275 MHz ainsi qu'une bande entre 415 MHz et 425 MHz.

D'autres systèmes comme le NTT (Nippon Telephone and Telegraph) au Japon ; étaient basés sur cette technique de première génération [2].

Ces systèmes reposaient sur une modulation analogique de fréquence FM (Frequency Modulation) et un mode d'accès de type FDMA (Frequency Division Multiple Access) où une fréquence est allouée à un utilisateur, ce qui limitait considérablement le nombre d'utilisateurs.

L'arrivée des technologies numériques a résolu ce problème, permettant ainsi l'essor de ce moyen de communication, et rendant obsolète cette génération.

#### I.3.2. Deuxième génération « 2G »

La seconde génération de réseaux mobiles (notée 2G) a marqué une rupture avec la première génération (1G) de téléphones cellulaires grâce au passage de l'analogique vers le numérique. Ce sont toujours les transmissions de la voix qui dominent mais les demandes pour les fax, messages courts et transmissions de données ont augmenté rapidement. Le développement des cellulaires de seconde génération fut dirigé par le besoin d'améliorer la qualité de transmission, les capacités du système ainsi que la couverture du réseau. Les technologies des semi-conducteurs et des dispositifs à micro-ondes ont permis l'utilisation de la transmission digitale au sein des télécommunications mobiles.

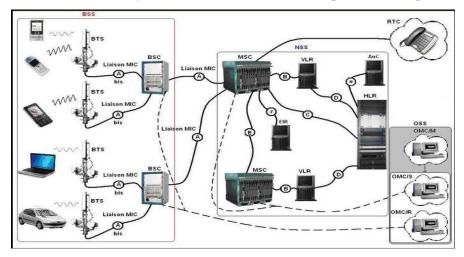

Aujourd'hui de nombreux standards liés au 2G sont apparus et sont utilisés dans le monde entier. Chaque standard à son propre niveau de mobilité, de capacité et de service. Certains standards ne sont utilisés que dans un pays ou région et sont pour la plupart incompatibles entre eux. Le réseau GSM [2] (Global System for Mobile communications) constitue au début du 20ème siècle le standard de téléphonie mobile le plus utilisé en Europe. Baptisé (Groupe Spécial Mobile) à l'origine de sa normalisation en 1982, il est devenu une norme internationale nommée (Global System for Mobile communications) en 1992. Le GSM fonctionne suivant un mode d'accès multiple à répartition dans le temps ou TDMA (Time Division Multiple Access) avec une modulation de type GMSK (Gaussian Minimum Shift Keying). La figure suivante schématise

l'architecture générale du réseau GSM en englobant les trois sous systèmes ainsi que les différentes liaisons entre les différents sous systèmes et les liaisons entres des parties de chaque sous système

Figure I.1. Architecture du réseau GSM.

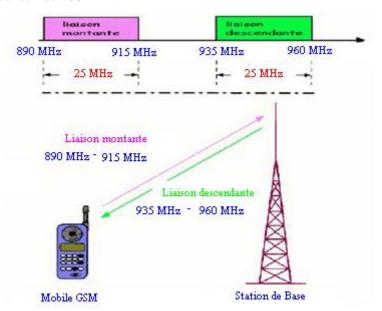

Deux bandes de fréquences distinctes sont dédiées à la réception et à l'émission (Figure I.2). La liaison montante se fait de 890 à 915MHz et la liaison descendante de 935 à 960MHz. Chaque bande est divisée en canaux de 200KHz.

**Figure I.2**. Liaison montante et descendante du GSM.

Chaque canal émet ou reçoit pendant une durée de temps appelée trame (Figure I.3), chacune est divisée dans le temps et l'on attribue aux utilisateurs des courts intervalles ou slots, pendant lesquels ils peuvent communiquer. Dans le cas du GSM les trames sont de 4,615 ms et sont divisées en 8 slots de 577  $\mu$ s, ce qui permet à huit utilisateurs de communiquer successivement sur le même canal.

Figure I.3. Structure d'une trame de GSM.

La norme GSM autorise un débit maximal de 9,6 kbps, ce qui permet de transmettre la voix ainsi que des données numériques de faible volume, par exemple des messages textes SMS (Short Message Service) ou des messages multimédias MMS (Multimédia Message Service).

D'autres normes reprennent ces caractéristiques mais à des fréquences supérieures comme la norme DCS 1800 (Digital Cellular System) dans la bande de fréquences des 1800 MHz en Europe, utilisant la bande [1710-1785] MHz à l'émission et [1805-1880] MHz comme bande de réception; et la norme PCS 1900 (Personal Communication Service) dans la bande de fréquences des 1900 MHz [2].

Aux Etats-Unis, la seconde génération de téléphonie mobile est apparue avec les normes IS 136 ou DAMPS (Digital Advanced Mobile Phone System) évolution de la norme analogique AMPS, IS 54 également appelée NADC (North American Digital Cellular), et IS 95 encore dénommée CDMA One. Ces normes partagent les mêmes bandes de fréquences entre 824 MHz et 849 MHz à l'émission, et entre 869 MHz et 894 MHz à la réception. Elles diffèrent notamment par leur technique d'accès, le nombre de canaux et l'espacement entre ceux-ci.

Au Japon, la seconde génération a été marquée par l'arrivée de la norme PDC (Personal Digital Cellular). Ses bandes émettrices et réceptrices sont divisées en deux, une partie centrée autour de 800 MHz et une autre autour de 1500 MHz [2].

#### I.3.3. Le GPRS « 2.5G »

Des améliorations de la norme GSM sont mises au point afin d'en améliorer le débit. C'est le cas notamment des standards GPRS (General Packet Radio Service) 2,5G; et le EDGE (Enhanded Data Rate for GSM Evolution) 2,75G. Ces deux standards continuent à profiter de l'infrastructure existante du GSM.

Le GPRS fait son apparition en 2001. Il permet d'étendre l'architecture du standard GSM, afin d'autoriser le transfert de données par paquets avec des débits qui peuvent dépasser les 100 kbit/s (au lieu de 9,6 kbit/s pour le GSM).

#### I.3.4. Entre la 2,5G et la 3G : EDGE « 2,75G »

Tout comme le GPRS, le standard EDGE est utilisé comme transition vers la troisième génération mobile (3G). Il utilise une nouvelle modulation de type 8 PSK (Phase Shift Keying), optimisant le débit efficace à l'interface GSM, permettant d'atteindre des débits de 384 Kbits/s au maximum [3].

Les différents continents ont développé des systèmes assez similaires dans le principe, mais parfois différents dans leur réalisation. C'est donc dans le cadre d'une homogénéisation globale des standards qu'est née l'idée d'une troisième génération de systèmes cellulaires.

#### I.3.5. Troisième génération « 3G »

Depuis 1985, l'Union Internationale de Télécommunications (UIT, ou ITU en anglais) réfléchit à un système de troisième génération, initialement appelé Futur Public Land Mobile Telephone System FPLMTS, mais actuellement connu sous le nom d'IMT 2000.

L'idée fondatrice du système 3G est d'intégrer tous les réseaux de deuxième génération du monde entier en un seul réseau et de lui adjoindre des capacités multimédia (haut débit pour les données). Le principe du système est souvent résumé dans la formule *anyone*, *anywhere*, *anytime*, signifiant que chacun doit pouvoir joindre ou être joint n'importe où et n'importe quand. Le système doit donc permettre l'acheminement des communications indépendamment de la localisation de l'abonné, que celui-ci se trouve chez lui, au bureau, en avion....

Le choix de la technologie 3G prendra en considération des facteurs techniques, politiques et commerciaux. Les facteurs techniques concernent la fourniture des débits demandés et la performance du réseau. Politiquement, les différents organismes de normalisation doivent parvenir à un accord et prendre en compte les spécificités régionales. Enfin, les investissements engagés par les opérateurs dans les systèmes existants laisseraient à penser qu'il faut choisir un système 3G compatible avec les réseaux 2G, tandis que bien sûr les constructeurs pencheraient plutôt pour un nouveau système qui leur ouvrirait de belles opportunités commerciales.

La troisième génération ne repose pas sur une interface de communication unique et mondiale mais sur plusieurs interfaces [5], plus ou moins compatibles, regroupées sous le nom IMT 2000. Il regroupe des systèmes comme, en Europe ou au Japon : l'UMTS (Universal Mobile Telephone System) également appelé W-CDMA, aux Etats-Unis ; le CDMA 2000, ou encore le TD-SCDMA en Chine.

Alors L'UMTS (Universal Mobile Telecommunication System) est la version européenne de l'IMT2000 (International Mobile Telecommunication), la norme mondiale pour ces systèmes de troisième génération.

Le marché visé n'est plus seulement celui de la radiotéléphonie mais celui du multimédia mobile, avec notamment l'accès à haut débit à Internet sur un terminal portatif mobile ou la transmission en temps réel d'images haute résolution et de vidéos.

Les autres principales caractéristiques à respecter sont :

- l'assurance en mobilité d'un débit de 144 kbits/s (de préférence 384 kbits/s) partout où le service est assuré ;

- l'assurance dans certaines zones (de mobilité limitée) d'un débit de 2 Mbits/s ;

- une haute efficacité spectrale par rapport aux systèmes 2G;

- une haute flexibilité pour permettre aisément l'introduction de nouveaux services.

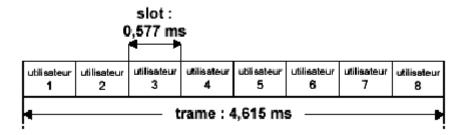

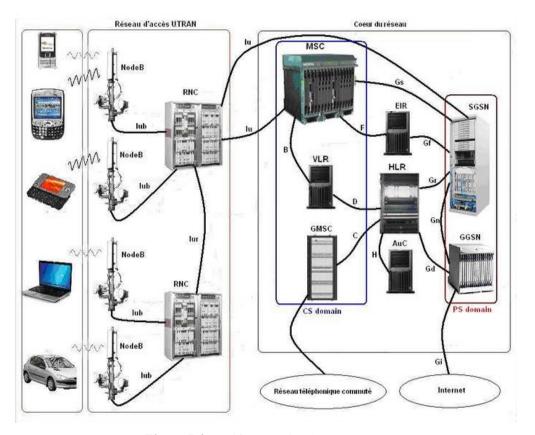

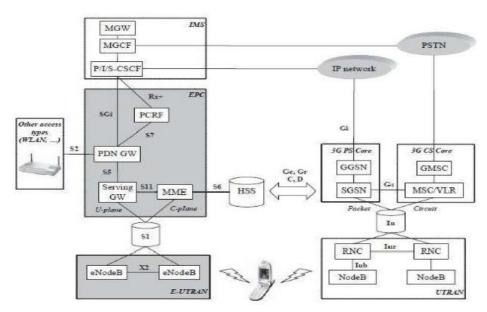

#### I.3.5.1. Architecture

Comme le montre la figure I.4, le réseau UMTS est composé d'un réseau d'accès UTRAN (UMTS Terrestrial Radio Access Network) et d'un réseau cœur.

Figure I.4. Architecture du réseau UMTS.

#### I.3.5.2. Organisation fréquentielle

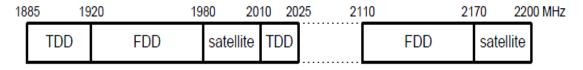

Les bandes de fréquences allouées pour l'IMT 2000 sont 1885-2025 MHz et 2110-2200 MHz [6]. La figure I.5 représente l'utilisation de la bande de fréquences pour l'UMTS.

TDD: Time Division Duplex

FDD: Frequency Division Duplex

Figure I.5. Utilisation de la bande de fréquences pour l'UMTS.

#### I.3.5.3. Organisation temporelle

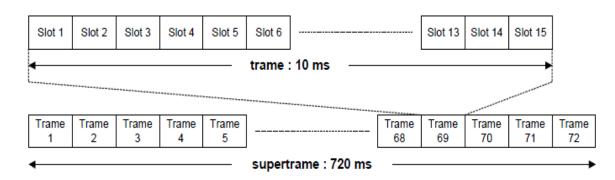

L'organisation temporelle de l'UMTS est basée sur une supertrame de 720 ms, comportant elle-même 72 trames. Chaque trame de 10 ms est divisée en 15 slots de 667 µs [7]. Cette organisation est présentée par la figure suivante

**Figure I.6.** Structure de trame de l'UMTS.

#### I.3.5.4. Le mode d'accès

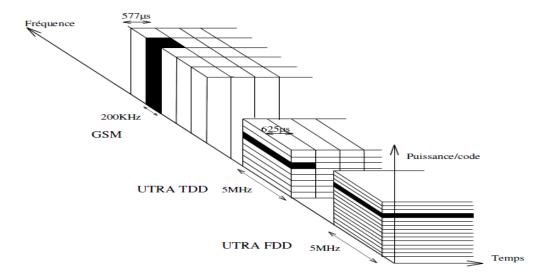

L'UMTS fonctionne suivant le mode d'accès multiple à répartition par les codes (CDMA). Les signaux provenant de différents mobiles coexistent dans un même canal mais la technique d'étalement de spectre permet de leur attribuer des codes différents. Le principe consiste à multiplier les signaux par des séquences binaires pseudo-aléatoires différentes à haut-débit (séquence directe ou DS-CDMA) [5]. L'information est étalée sur 5MHz approximativement d'où le nom de Wideband (WCDMA).

L'UMTS Terrestrial Radio Access (UTRA) possède deux modes de duplexage, FDD (Frequency Division Duplex) et TDD (Time Division Duplex) comme le montre la figure I.7. Le mode FDD est réservé pour les bandes de fréquences appariées du système, i.e. une bande dédiée à la réception et une bande dédiée à l'émission. Le mode TDD est réservé pour les bandes de fréquences non-appariées du système, i.e. liaison montante et liaison descendante sont portées sur la même fréquence [8]. Durant la communication on attribue à tour de rôle des intervalles de temps pour l'émission et des intervalles de temps pour la réception. La modulation spécifiée pour l'UMTS en réception est la QPSK (Quadrature Phase Shift Keying).

Figure I.7. Techniques d'interface radio pour le GSM et l'UMTS.

L'UMTS est conçu pour pouvoir s'interconnecter et interagir avec le GSM dans toutes ses phases d'évolution. Aussi, l'UMTS peut être considéré comme l'étape la plus porteuse en termes d'innovations technologiques. Ce système se distingue en effet de ses prédécesseurs HSCSD (High Speed Circuit Switched Data), GPRS et EDGE, par des débits maximum plus élevés de 2 Mbit/s, et utilise des canaux de 5 MHz de large.

Grâce à sa vitesse accrue de transmission de données, l'UMTS ouvre la porte à des applications et services nouveaux. L'UMTS permet en particulier de transférer dans des temps relativement courts des contenus multimédia tels que les images, les sons et la vidéo. Les nouveaux services concernent surtout l'aspect vidéo : Visiophonie, MMS Vidéo, Vidéo à la demande, Télévision.

#### **I.3.6.** Le HSDPA « 3.5 G »

Au même titre que le GPRS et EDGE ont permis, sans modifier le principe de base des communications, à leur génération de systèmes cellulaires d'évoluer en terme d'efficacité. Le HSDPA (High-Speed Downlink Packet Access) est déjà considéré comme le standard 3.5G des télécommunications mobiles [4]. Le HSPDA, grâce à sa modulation en 16-QAM, autorise des débits de 10 Mbits/s. Ainsi, grâce à l'introduction de la nouvelle modulation 64-QAM, le débit théorique de 14 Mbits/s est possible par le réseau HSDPA.

#### I.3.7. Le HSUPA « 3.75 G »

3,75G (3G++), encore appelé HSUPA, cette technologie mobile est une évolution de l'HSDPA, à laquelle on s'est efforcé d'optimiser le débit montant (upload). Ce qui nous permet d'avoir un débit montant à 5,8 Mbps théorique qui permet d'envoyer des fichiers/images/vidéo plus rapidement sur le réseau [9].

## I.3.8. Quatrième génération « 4G »

Toujours en cours de développement, le réseau 4G (4ème génération) [10]-[14] est proposé comme future génération des réseaux mobiles après la 3G. Ce réseau a également pour objectif d'abolir les frontières de la mobilité.

Avec le réseau 4G, un utilisateur peut se connecter où qu'il se trouve: à l'intérieur des bâtiments avec les technologies Bluetooth, UWB ou Wi-Fi..., à l'extérieur (dans la rue et les lieux publics) avec l'UMTS ou le WiMAX...

En général, le passage d'un réseau à l'autre deviendra transparent pour l'utilisateur. Les débits supposés sont entre 20 et 100 Mb/s à longue portée et en situation de mobilité, et 1 Gb/s à courte portée vers des stations fixes. Par définition, la 4G assure la convergence de la 3G avec les réseaux de communication radio fondés sur le protocole IP. La connexion devra être possible quel que soit le mode de couverture.

L'institution internationale de standardisation ITU (Union Internationale des Télécoms) n'a toujours pas donné de définition à la 4G. Les trois technologies supposées comme candidates potentielles pour une validation 4G sont [15]:

- Long Term Evolution (LTE) poussée par les Européens, avec Ericsson en tête suivi de Nokia et Siemens...

- **WiMAX version 802.16m** soutenu par Intel sachant que le WIMAX a été ajouté à la liste des standards 3G par l'ITU le 19/10/2007 [16].

- Ultra Mobile Broadband (UMB) soutenu par le fondeur américain Qualcomm (fabriquant des puces).

#### I.4. Présentation de la norme LTE

#### I.4.1. Introduction

Le LTE (Long Term Evolution of 3G) [17]-[23] est la norme de communication mobile la plus récente qui est proposée par l'organisme 3GPP dans le contexte de la 4G. Comme l'IEEE 802.16m, elle propose des débits élevés pour le trafic temps-réel, avec une large portée.

Le LTE comprend une interface radio qui a fait ses preuves dans les réseaux terrestres numériques de radiodiffusion et qui a été optimisée pour la radiocommunication mobile. Son utilisation implique le réaménagement des stations existantes, la mise en place de stations de base supplémentaires et la création de nouveaux terminaux mobiles qui supportent le LTE. Le LTE présente de multiples qualités, en particulier des débits élevés entre la station de base et les terminaux. Cela augmente la capacité de transmission et permet ainsi d'offrir le même débit à davantage d'utilisateurs ou de fournir des débits plus élevés au même nombre d'utilisateurs. En

outre, la réduction de l'intervalle de transmission des données (latence) devrait améliorer considérablement la réactivité du réseau. Enfin, le LTE devrait consommer moins d'énergie que l'UMTS, notamment au niveau du terminal; son autonomie s'en trouve rallongée, malgré la connexion à un service de données à large bande.

#### I.4.2. L'évolution du standard LTE

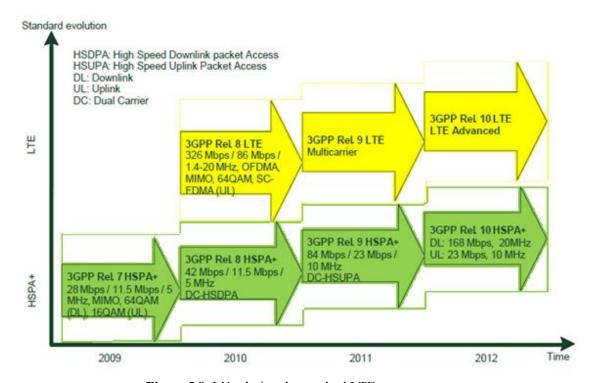

L'introduction du LTE a débuté en 2010. En voici les étapes [9].

**Figure I.8.** L'évolution du standard LTE.

Selon une mise à jour du rapport de l'évolution du LTE publié le 5 janvier 2012 ; la GSA (Global mobile Suppliers Association) confirme 49 réseaux LTE commerciaux dans le monde. 285 opérateurs, se sont engagés à des déploiements de réseaux commerciaux LTE ou sont engagés pour des essais ou étude de cette technologie. Le rapport GSA couvre les modes FDD et TDD du système LTE. La GSA a prévue pour fin 2012, un total de 119 réseaux commerciaux LTE dans plus de 50 pays [9].

Figure I.9. Réseaux LTE commerciaux et déclarations d'intention pour le LTE.

#### I.4.3. Architecture générale

La figure ci-dessous décrit l'architecture globale du réseau, en incluant non seulement le réseau Cœur et le réseau d'accès, mais aussi d'autres blocs, et cela dans le but de montrer la relation entre eux. Les nouveaux blocs spécifiés pour le LTE, connu aussi sous le nom d'EPS (Evolved Packet System), sont l'EPC (Evolved Packet Core) et l'E-UTRAN (Evolved UTRAN).

D'autres blocs sont également affichés, comme l'UTRAN (le réseau d'accès de l'UMTS), les deux parties PS et CS du réseau cœur, reliés respectivement, au réseau d'IP public (ou privé) et au réseau du téléphone.

Figure I.10. Architecture du LTE.

Le seul inconvénient de cette nouvelle technologie est l'installation de ses nouveaux équipements qui sont différents de ceux des normes précédentes, et le développement des terminaux adaptés.

#### I.4.4. Réseau d'accès (Access Network)

#### I.4.4.1. Caractéristiques

#### a. Débit de l'interface radio

L'interface radio E-UTRAN doit pouvoir supporter un débit maximum instantané de 100 Mbit/s en considérant une allocation de bande de fréquence de 20 MHz pour le sens descendant et un débit maximum instantané de 50 Mbit/s en considérant aussi une allocation de bande de fréquence de 20 MHz pour le sens montant. Les technologies utilisées sont OFDMA (Orthogonal Frequency Division Multiple Access) pour le sens descendant et SC-FDMA (Single Carrier - Frequency Division Multiple Access) pour le sens montant.

#### b. Délai pour la transmission de données

Moins de 5 ms entre l'UE et l'Access Gateway, en situation de non-charge où un seul terminal est ACTIF sur l'interface radio. La valeur moyenne du délai devrait avoisiner les 25 ms en situation de charge moyenne de l'interface radio. Ceci permet de supporter les services temps réel IP, comme la voix sur IP et le streaming sur IP.

#### c. Mobilité

Assurée à des vitesses comprises entre 120 et 350 km/h. Le handover pourra s'effectuer (le LTE ne permet que le hard handover et non pas le soft handover) dans des conditions où l'usager se déplace à grande vitesse.

#### d. Coexistence et Interfonctionnement avec la 3G

Le handover entre E-UTRAN (LTE) et UTRAN (3G) doit être réalisé en moins de 300 ms pour les services temps-réel et 500 ms pour les services non temps-réel. Il est clair qu'au début du déploiement du LTE, peu de zones seront couvertes. Il s'agira pour l'opérateur de s'assurer que le handover entre la LTE et la 2G/3G est toujours possible. Le handover pourra aussi s'effectuer entre le LTE et les réseaux CDMA-2000 [1].

### e. Flexibilité dans l'usage de la bande

E-UTRAN doit pouvoir opérer dans des allocations de bande de fréquence de différentes tailles incluant 1.25, 2.5, 5, 10, 15 et 20MHz.

#### f. Couverture de cellule importante dans les zones urbaines et rurales

Comme le LTE pourra opérer sur des bandes de fréquences diverses et notamment basses comme celle des 700 MHz, il sera possible de considérer des cellules qui pourront couvrir un large diamètre.

#### I.4.4.2. L'Interface Radio du LTE

Le LTE a introduit un certain nombre de nouvelles technologies, permettant l'emploie efficace du spectre et fournissant des débits beaucoup plus élevés. Ainsi, le LTE a utilisé la technologie OFDM (Orthogonal Frequency Division Multiplex) en tant que porteur du signal et les régimes d'accès associés, OFDMA (Orthogonal Frequency Division Multiplex Access), SC-FDMA (Single Frequency Division Multiple Access) et MIMO (Multiple Input Multiple Output). Les travaux sur le LTE ont débuté en décembre 2004 avec une étude de faisabilité (Release 7). La norme LTE est une évolution des normes de téléphonie mobile qui vise des débits élevés, elle s'appuie sur l'infrastructure du réseau UMTS déjà en place. Le LTE supporte les duplexages TDD et FDD et utilise les bandes de fréquence déjà allouées à l'UMTS (Release 8). Il y a 15 bandes de fréquences (bandes 1 à 14 et bande 17) qui utilisent le duplexage FDD et 8 bandes (33 à 40) qui utilisent le duplexage TDD (Tableau I.1). LTE a l'avantage de s'adapter aux anciennes normes existantes. La transition est donc possible avec l'UMTS FDD (W-CDMA), l'UMTS TDD et le GSM/EDGE.

| Band  | Frequencies UL/DL (MHz) |

|-------|-------------------------|

| 33.34 | 1900-1920               |

|       | 2010-2025               |

| 35.36 | 1850-1910               |

|       | 1930-1990               |

| 37    | 1910-1930               |

| 38    | 2570-2620               |

| 39    | 1880-1920               |

| 40    | 2300-2400               |

| Band | Frequencies UL/DL (MHz) |

|------|-------------------------|

| 1    | 1920-1980/2110-2170     |

| 2    | 1850-1910/1930-1990     |

| 3    | 1710-1785/1805-1880     |

| 4    | 1710-1755/2110-2155     |

| 5    | 824-849/869-894         |

| 6    | 830-840/875-885         |

| 7    | 2500-2570/2620-2690     |

| 8    | 880-915/925-960         |

| 9    | 1750-1785/1845-1880     |

| 10   | 1710-1770/2110-2170     |

| 11   | 1428-1453/1476-1501     |

| 12   | 698-716/728-746         |

| 13   | 777-787/746-756         |

| 14   | 788-798/758-768         |

| 15   | 704-716/734-746         |

a- Les bandes TDD

**b-** Les bandes FDD

**Tableau I.1.** Allocation de fréquences pour le LTE

Le tableau I.2 récapitule l'évolution des standards de communication.

| Génération | Norme européenne | Caractéristiques                            | Année     |

|------------|------------------|---------------------------------------------|-----------|

| 1G         | ETACS            | Analogique : premier téléphone sans fil,    | 1980      |

|            |                  | voix uniquement.                            |           |

| 2G         | GSM              | Permet le transfert de voix ou de données   | 1990-2000 |

|            |                  | numériques de faible volume.                |           |

| 2.5G       | GPRS             | Permet le transfert de voix ou de données   | 1990-2000 |

|            |                  | numériques de volume modéré.                |           |

| 2.75G      | EDGE             | Permet le transfert simultané de voix et de | 1990-2000 |

|            |                  | données numérique.                          |           |

| 3G         | UMTS             | Permet le transfert simultané de voix et de | 2000-2010 |

|            |                  | données numérique à haute débit.            |           |

| 3.5G/3G+   | HSDPA            | Permet d'atteindre des débits supérieurs    | 2000-2010 |

|            |                  | dans la voie descendante en mode            |           |

|            |                  | paquets.                                    |           |

| 3.75G/3G++ | HSUPA            | Une variante de HSDPA sur la voie           | 2000-2010 |

|            |                  | montante.                                   |           |

| 4G         | LTE, WIMAX       | Le débit sera encore augmenté : système     | 2010      |

|            | •                | multi-antennes devraient être utilisé.      |           |

**Tableau I.2.** L'évolution des standards de radiocommunication.

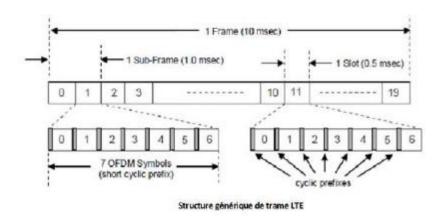

#### I.4.4.3. La structure des trames en LTE

Les trames LTE sont de 10 ms. Ils sont divisés en 10 sous-trames, chaque sous-trame de longueur 1,0 ms. Chaque sous-cadre est divisée en deux slots, chacun de 0,5 ms. Un slot est composé de 6 ou 7 symboles OFDM, selon que le préfixe cyclique normal ou étendu est employé.

Figure I.11. Structure générique de trame LTE.

#### I.5. Comparaison UMTS et LTE

Les deux normes de réseaux mobiles répondent aux même objectifs définit par l'ITU (International Telecommunication Union) :

- Supporter les applications multimédia : les terminaux auront la capacité d'accepter simultanément des services de natures différentes (voix, visiophonie, navigation web, transfert de fichier).

- Supporter des débits plus élevés par rapport à ceux enregistré par les normes de 2G.

- Permettre d'augmenter la palette de service proposé aux utilisateurs.

- Transparence du réseau pour l'usager : l'usager ne doit pas se rendre compte qu'il passe d'un réseau à un autre.

En fait, les deux normes ont respecté les objectifs imposés par ITU mais LTE est une évolution de la norme UMTS ce qui concerne les débits, les délais de latence et les technologies utilisés.

#### I.6. Conclusion

A travers ce premier chapitre, nous avons présenté un état de l'art des standards de téléphonie mobile. Les déploiements des réseaux 3G, 3,5G, et 4G, quelle que soit la famille technologique retenue (UMTS, LTE, etc.), constituent l'enjeu technologique majeur de cette décennie. Dans le cadre de ce mémoire, la norme LTE qui devrait permettre aux services de communication cellulaires d'aller de l'avant dans un futur proche, est détaillée à la fin de ce chapitre. Le chapitre suivant sera consacré à une étude détaillée des différentes techniques de synthèse de fréquences en mettant en évidence une description générale de chaque bloc constituant le synthétiseur de fréquences que nous allons concevoir dans le cadre des travaux de ce mémoire.

#### II. 1. Introduction

La synthèse de fréquence est une fonction clé dans les architectures de circuits électroniques (et plus précisément dans les récepteurs et émetteurs des ensembles de communication) dont le rôle est de fournir des signaux périodiques. Elle consiste à générer à partir d'un signal fourni par un oscillateur de référence, un signal de fréquence différente. La stabilité de fréquence de l'oscillateur de référence est alors transférée au signal synthétisé. Dans ce chapitre, nous allons décrire dans un premier temps les spécifications générales d'un synthétiseur de fréquence. Nous nous intéresserons par la suite aux différentes techniques les plus courantes de synthèse disponibles en littérature. Pour finir, nous présenterons une étude plus détaillée de la PLL, et de tout ses composants : comparateur de phase, pompe de charges, filtre de boucle, oscillateurs et diviseur de fréquences [2].

#### II.2. Rôle de l'oscillateur local (LO) dans un transmetteur/récepteur

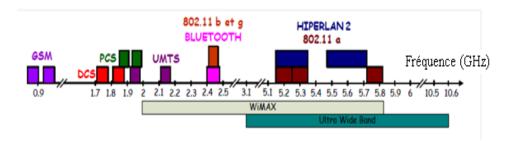

Un système de radiocommunication est un système de communication qui utilise les ondes hertziennes comme moyen de transmission. Les systèmes de radiocommunication sont nombreux et leurs applications très diverses : radiodiffusion, télévision, téléphonie, réseaux locaux de transmission de données numériques, etc...

Dans le cas des circuits radiofréquences modernes, on cherche généralement à couvrir de multiples standards de télécommunications. La figure II.1 présente une illustration des principaux standards dans une bande comprise entre 0,8 et 10 GHz.

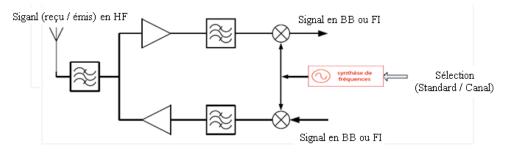

Figure II.1. Illustrations des standards de communication dans la bande 0,8-10 GHz.

Donc, pour les systèmes fonctionnant avec plusieurs de ces standards (multistandards) ou pour ceux fonctionnant sur différents canaux d'un même standard il sera nécessaire que le synthétiseur de fréquences couvre une large plage de fréquences ou alors plusieurs sous-plages de fréquences. Pour ce faire, nous utilisons une chaîne d'émission/réception comme celle présentée à la figure II.2 où les différents éléments sont reconfigurables. Le signal de sortie du synthétiseur est communément appelé Oscillateur Local (OL) car il intervient dans les systèmes de communication comme oscillateur de référence pour la translation de fréquence : des Hautes Fréquences (HF) vers

la Bande de Base (BB) ou la Fréquence Intermédiaire (FI) en réception, et BB ou FI vers HF en émission [5].

Figure II.2. Rôle du synthétiseur de fréquence dans un émetteur-récepteur RF.

L'utilisation d'un oscillateur contrôlé par tension VCO (Voltage Controlled Oscillator) seul pour la génération des fréquences requises par l'Oscillateur Local (OL) dans la chaine d'émission/réception, n'est pas une solution envisageable, bien que très attrayante du point de vue de la complexité et de la consommation de puissance. Ceci s'explique parce que la précision requise des fréquences générées par l'oscillateur local est très sévère, et la stabilité en fréquence d'un VCO en oscillation libre est très mauvaise. Elle est affectée à court terme par le bruit de phase, et à long terme par les variations de température, le vieillissement, les changements de conditions de polarisation, etc.

#### II.3. Synthèse de fréquence

Pour pallier à ces difficultés, le VCO peut être imbriqué dans une boucle de rétroaction visant à asservir la phase instantanée de son signal de sortie à celle d'un signal de référence très pur. Cette configuration est appelée boucle à verrouillage de phase (Phase-Locked Loop - PLL). La naissance de la PLL remonte à 1932, alors qu'un ingénieur nommé De Bellescize cherchait à améliorer la réception des signaux radioélectriques en modulation d'amplitude. A cette époque, les réalisations à base de PLL étaient volumineuses et chères, c'est pourquoi ce principe a longtemps été réservé aux matériels professionnels jusqu'à la généralisation des circuits intégrés dont l'arrivée a bouleversé toutes les branches de l'électronique.

#### II.4. Critères de performance des synthétiseurs de fréquences

Lors de la conception d'un synthétiseur de fréquences pour la génération de la porteuse d'un transmetteur/récepteur RF, plusieurs critères de performance doivent être satisfaits afin que le système soit conforme à une norme de communication donné.

Les normes de communication, tels que GSM, Bluetooth, et LTE définissent un ensemble de limitations, paramètres et bancs d'essais à respecter afin que le système de communication puisse être utilisé de façon sécuritaire et sans impacts négatifs sur les communications des autres usagers. Des spécifications précises pour les différents blocs d'un système de communication RF peuvent être extraites de ces normes.

Dans le cas d'un synthétiseur de fréquences, les spécifications concernent principalement sa pureté spectrale, son bruit de phase et son temps d'établissement [2]. Dans les sections qui suivent, nous allons présenter les différents critères de performance d'un synthétiseur.

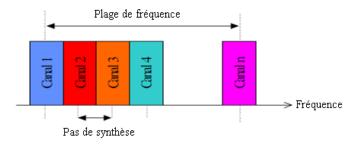

#### II.4.1. Plage de fréquences et pas de synthèse

La principale caractéristique d'un synthétiseur de fréquences est l'ensemble des fréquences qu'il peut générer. Pour une utilisation dans un émetteur-récepteur radio, les fréquences à couvrir sont fixées par le ou les standard(s) de communication que l'ont souhaite pouvoir couvrir (plan de fréquences).

La plage de fréquences est donc, la zone comprise entre la plus petite et la plus grande des fréquences synthétisables, sa largeur doit être supérieure ou égale à la bande de fréquences allouée au standard de communication.

Figure II.3. Plage de fréquences et pas de synthèse.

Le pas de synthèse est la différence de fréquence entre deux fréquences synthétisées consécutives. Habituellement le pas de synthèse est inférieur ou égal à la largeur d'un canal, de façon à pouvoir opérer sur tous les canaux du standard de télécommunication. En général, la complexité du synthétiseur de fréquences est fortement dépendante du plan de fréquences du standard de télécommunication [2].

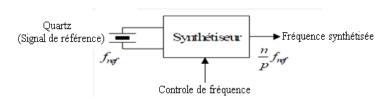

Figure II.4. Synthétiseur et pas de fréquences.

Le pas de fréquence est dépendant de la fréquence de référence du synthétiseur. Usuellement, la fréquence synthétisée est une fraction (division de deux nombres entiers) de la fréquence de référence (Figure II.4). La fréquence de référence doit donc être choisie avec soin, afin de permettre d'obtenir la plage de fréquences et le pas de synthèse voulus.

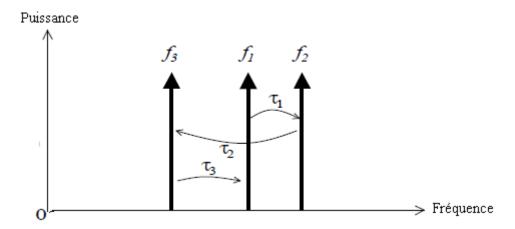

## II.4.2. Le temps d'établissement et la bande passante

De nombreux standards de communication nécessitent que le synthétiseur de fréquences soit capable de changer rapidement de fréquence. Le temps d'établissement représente le temps nécessaire au synthétiseur pour générer une fréquence prédéterminée. Pour un système multistandard, cela peut se définir comme le temps maximal nécessaire pour atteindre un offset de fréquence donné par rapport à la fréquence désirée [5]. Un exemple, où le synthétiseur bascule entre trois fréquences, est présenté à la figure II.5.

Figure II.5. Exemple de basculement du synthétiseur entre trois fréquences.

D'un point de vue fréquentiel, ce temps d'établissement va être directement lié à la bande passante du synthétiseur de fréquence utilisé. Plus la bande passante d'une architecture d'oscillateur locale sera grande, plus ce système sera capable de s'accrocher rapidement autour d'une fréquence donnée et pourra diminuer l'erreur de phase. Cependant, la bande passante du synthétiseur ne pourra être augmentée que dans les limites fixées par les conditions de stabilité du système. Cette limite, qui est fonction des différents blocs du synthétiseur, est, en théorie, fixée à la valeur de la fréquence de référence d'entrée du synthétiseur divisée par 10. Cependant, dans la pratique, cette valeur est généralement encore divisée d'un facteur 10 à 20 afin de diminuer les dérives de la tension de contrôle de l'oscillateur et d'en accroitre le taux de réjection.

#### II.4.3. Pureté spectrale

Idéalement, un synthétiseur de fréquences devrait générer un signal purement sinusoïdal, sans bruit ou parasite. Il en est autrement en pratique. Un premier défaut est la génération de raies parasites (spurious ou spurs dans la littérature anglophone) dans le spectre du signal synthétisé [5]. Souvent, à la place d'une raie unique à la fréquence synthétisée, on retrouve un ensemble de raies parasites de faibles puissances. Un exemple d'un tel spectre est présenté à la figure II.6.

**Figure II.6.** Exemple de spectre généré par un synthétiseur de fréquences.

De plus, on trouve habituellement dans le spectre de sortie, des harmoniques du signal synthétisé. En effet le signal généré est rarement sinusoïdal. A plus basse fréquence on peut également trouver une raie à la fréquence de référence. Ces raies parasites étant relativement loin en fréquence de la fréquence synthétisée, on peut assez facilement les supprimer à l'aide d'un bon filtre.

En sortie des synthétiseurs, on trouve également des raies parasites situées à proximité de la fréquence synthétisée. Celles-ci sont en général les plus gênantes. Elles ne peuvent être supprimées par un simple filtre : Il sera alors nécessaire d'utiliser un filtre très sélectif, d'ordre élevé, et par conséquent très encombrant. Il est donc nécessaire de minimiser ces raies parasites à la source, c'est-à-dire au niveau du synthétiseur.

Les sources de ces raies parasites sont habituellement multiples : Une modulation de phase ou de fréquence fortuite, une erreur de phase statique ou un couplage de différents signaux [5].

#### II.4.4. Bruit de phase

Une seconde source de dégradation du spectre synthétisé est également à l'œuvre dans les synthétiseurs de fréquences : le bruit généré par les composants actifs et passifs des circuits. Ces bruits en tension et courant des composants se traduisent par du bruit sur l'amplitude et sur la phase du signal généré par le synthétiseur.

Le bruit de phase appelé aussi **SSBPN** (Single Side Band Phase Noise) est généralement caractérisé dans le domaine fréquentiel. Il est la représentation d'une variation aléatoire de la phase du signal de sortie d'un oscillateur. Un oscillateur idéal peut être décrit par l'expression temporelle suivante :

$$V(t) = A.\sin(2\pi f_{OL}t + \theta)$$

(II.1)

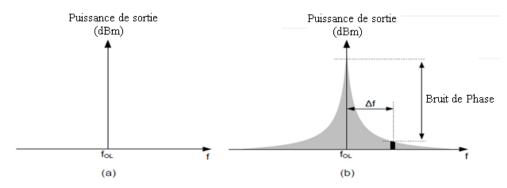

Les grandeurs A,  $f_{OL}$  et  $\theta$  représentent respectivement l'amplitude du signal, sa fréquence et sa phase. La figure II.7 (a) présente d'un point de vue fréquentiel le signal ainsi généré. Dans le cas réel, l'amplitude et la phase du signal ne sont pas constantes et subissent des variations aléatoires. L'expression réelle est donc la suivante :

$$V(t) = A(t).\sin(2\pi f_{0L}t + \theta(t))$$

(II.2)

En radio communication, les variations d'amplitude sont généralement négligeables. En revanche les variations de la phase entraînent une variation de la période du signal et donc de sa fréquence. Le bruit de phase de l'oscillateur, qui caractérise cette variation, est présenté sur la figure II.7 (b).

Figure II.7. Bruit de phase d'un oscillateur. (a) cas idéal. (b) cas réel.

Afin de quantifier le bruit de phase [9], considérons une bande unitaire de largeur 1 Hz située à un offset  $\Delta f$  de la fréquence  $f_{OL}$ . Le bruit de phase est alors égal au rapport de la densité spectrale de puissance de la bande unitaire sur la densité spectrale de puissance de la fréquence porteuse et s'exprime en dBc/Hz [24]:

$$BP(\Delta f) = 10.\log \left[ \frac{P_{bande} (f_{OL} + \Delta f, 1Hz)}{P_{porteuse}} \right]$$

(II.3)

Où:

$P_{bande}$  ( $f_{ol} + \Delta f$ , 1Hz): représente la densité spectrale de puissance de la bande unitaire.

**P**<sub>porteuse</sub>: représente la densité spectrale de la porteuse.

Dans un système radiofréquence, les performances d'un synthétiseur de fréquence en matière de bruit de phase sont critiques et ils dépendent du type d'application. Plus les canaux sont proches les uns des autres, plus les contraintes en terme de bruit sont importantes. Leurs conséquences sur la qualité de réception et d'émission sont nombreuses.

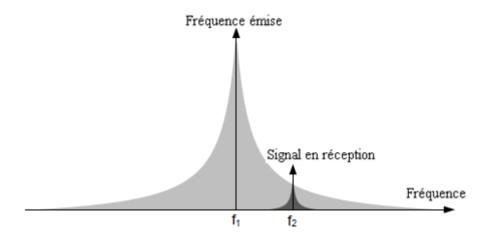

En émission, lors de la transposition du signal en haute fréquence, le bruit de phase de l'oscillateur va être transmis vers le signal de sortie. Si la fréquence de ce dernier se retrouve proche d'un canal de réception du même système radiofréquence ou d'un système voisin, il va alors le perturber. En effet, suite aux pertes dues à l'environnement de transmission, le signal reçu a une puissance très inférieure à celle du signal émis. Nous pouvons voir sur la figure II.8, qu'à la fréquence voisine  $f_2$ , le niveau de bruit de phase du signal émis à la fréquence  $f_1$  est si élevé qu'il masque le signal en réception. De plus, lors d'une transmission où une modulation de phase est

utilisée, le bruit de phase va perturber l'information, ce qui pourra entraîner une incertitude sur la décision lors de la démodulation augmentant en conséquence le taux d'erreur.

Figure II.8. Effet du bruit de phase en émission.

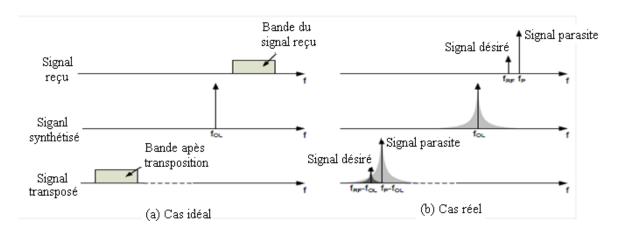

Lors de la réception d'un signal radiofréquence, le synthétiseur de fréquence va permettre de réaliser la conversion descendante du signal reçu en bande de base. Dans le cas idéal de la figure II.9 (a) où le signal d'oscillateur local est non bruité, le signal transposé ne comprend alors que l'information désirée.

Figure II.9. Effet du bruit de phase en réception. (a) cas idéal. (b) cas réel.

En revanche, si un signal parasite de fréquence proche du signal désiré est présent dans le spectre et dans le cas, plus réaliste, de la figure II.9 (b) d'un signal d'oscillateur local bruité, le signal désiré va donc être fortement dégradé par le bruit du signal parasite en bande de base. Ce phénomène est appelé « mélange réciproque » [25].

Enfin, pour les transmissions utilisant des modulations basées sur des variations de la phase instantanée (ex. modulation PSK), le bruit de phase de l'oscillateur peut entrainer une erreur d'interprétation lors de la démodulation du signal.

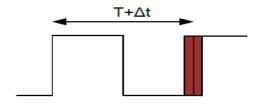

Dans le domaine temporel, la fluctuation aléatoire et dynamique de la période d'un signal est dénommée gigue temporelle (jitter) [9], [26]. La figure II.10 représente l'illustration de cette gigue temporelle.

Figure II.10. Illustrations de la gigue temporelle cycle à cycle.

Pour toutes les applications radiofréquences, les spécifications en bruit de phase sont fixées par les standards.

#### II.5. Techniques de synthèse de fréquence

Les techniques de synthèse de fréquence se différentient par les composants utilisés et par leurs performances en bruit. On rencontre trois principes [5] :

- la synthèse directe analogique qui existe depuis les années 1930,

- la synthèse indirecte à base de PLL (Phase Loocked Loop),

- la synthèse directe numérique DDS (Direct Digital Synthesis), plus récente qui n'a rien de commun avec les deux précédentes.

#### II.5.1. Synthèse directe analogique

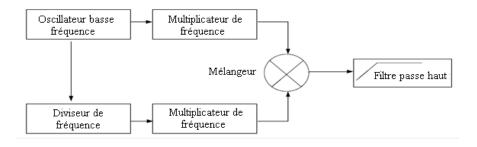

La synthèse directe analogique consiste, à partir d'une source unique stable, à générer, une série de fréquences multiples ou sous-multiples par multiplication et division puis de les combiner entre elles par soustraction et addition. L'intérêt principal de ce type de synthèse est de procurer un faible temps d'acquisition qui dépend essentiellement de la rapidité de commutations de fréquence [5]. Un exemple de synthèse analogique directe est décrit dans la figure II.11. Le principe de ce type de synthèse est de partir d'un oscillateur basse fréquence de haute stabilité et d'en diviser et multiplier la fréquence pour ensuite mélanger les deux fréquences résultantes et de filtrer le signal obtenu à l'aide d'un filtre passe-haut.

Figure II.11. Principe de la synthèse directe analogique.

Cette technique permet de réaliser des synthétiseurs avec un excellent bruit de phase, néanmoins au prix d'une importante surface d'intégration ainsi que d'une grande consommation. Aussi, pour réaliser un instrument couvrant une large gamme avec un faible pas de fréquence, la synthèse de fréquence directe réclame un nombre important de mélangeurs et de filtres.

On préfèrera toute fois la synthèse indirecte utilisant le principe de la boucle à asservissement de phase, à cause de sa simplicité de réalisation et de sa facilité de programmation [27]. De plus ne bénéficiant pas du filtrage inhérent à la boucle d'asservissement de phase, le spectre obtenu par synthèse directe peut contenir de nombreuses raies parasites aux fréquences d'intermodulation produites par les mélangeurs.

#### II.5.2. Synthèse directe numérique DDS (Direct Digital Synthesis)

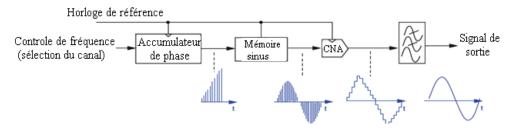

La synthèse directe numérique est une des techniques de synthèse de fréquence les plus récentes. Elle a été introduite en 1971 par J. Tierney [28]. Elle fonctionne sur le principe de la création d'un signal à partir d'échantillons en faisant varier leur nombre et ce à vitesse constante. Comme son nom l'indique, cette technique fait une utilisation massive de circuit numérique.

Figure II.12. Synthétiseur de fréquence à séquence numérique.

La solution numérique pour synthétiser une fréquence est décrite sur la figure II.12. Le mot appliqué à l'entrée de l'accumulateur de phase va permettre le contrôle de la fréquence de la manière suivante:

L'accumulateur de phase génère une rampe de phase périodique dépendante du mot d'entrée. Ce signal est ensuite injecté dans une mémoire afin d'affecter une amplitude à chaque valeur discrète de la rampe : les valeurs affectées dépendent d'un tableau d'adressage conçu de manière à générer une sinusoïde. Enfin, le signal de sortie de la mémoire sera ensuite traduit sous forme analogique à l'aide d'un convertisseur numérique analogique, puis filtré afin d'éliminer les harmoniques de la fréquence d'échantillonnage (et limiter la distorsion de la sinusoïde obtenue).

Considérons le mot d'entrée défini par l'entier M, et la taille de l'accumulateur par l'entier T, le tout étant contrôlé par l'horloge de fréquence  $f_{horl}$ , la fréquence du signal de sortie  $f_{out}$  est donnée par:

$$f_{OUT} = f_{horl} \cdot \frac{M}{T} (Hz)$$

(II.4)

Le pas de fréquence  $\Delta f$  est donc défini par:

$$\Delta f = \frac{f_{horl}}{T}(Hz) \tag{II.5}$$

Le premier inconvénient de la plupart des synthétiseurs numériques directs réside dans les niveaux des raies parasites causées par la quantification et la linéarité limitée du convertisseur numérique-analogique. Une règle de base assez grossière évalue le niveau de ces raies générées par la quantification du CNA à 6 fois le nombre de bits d'entrée (exemple : le niveau des raies de quantification d'un CNA 8-bits sera de 48dB inférieur au niveau de la porteuse) [28].

En outre, plus la fréquence d'horloge utilisée approche la fréquence maximale de fonctionnement du CNA plus les raies dues aux non-linéarités seront prédominantes. La fréquence de sortie du DDS est donc limitée par la fréquence de fonctionnement du CNA.

#### II.5.3. Synthèse indirecte à base de PLL (Phase Locked Loop)

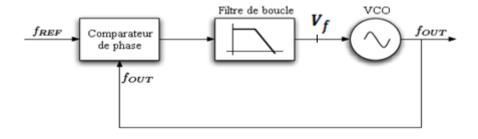

D'usage très répandu, la boucle à verrouillage de phase (PLL), est un circuit dans lequel est asservie la phase, et donc la fréquence, d'un oscillateur à celle d'une référence. La référence est le signal périodique appliqué en entrée, dont est dérivée la fréquence de sortie.

#### II.5.3.1. Principe global de fonctionnement de la boucle

Le principe général de fonctionnement est le suivant : le comparateur de phase compare la phase du signal de référence  $f_{REF}$  avec celle du signal à la sortie de la boucle,  $f_{OUT}$ , qui est égale à  $f_{VCO}$ . La sortie du comparateur de phase est une mesure du déphasage entre les deux signaux, et représente le signal d'erreur dans la boucle. Idéalement, l'effet de la rétroaction maintient les deux signaux  $f_{REF}$  et  $f_{OUT}$  à une différence de phase constante.

Puisque la boucle de rétroaction maintient une cohérence de phase entre ces deux signaux, ils oscillent donc à la même fréquence :  $f_{OUT}$  est donc verrouillée à  $f_{REF}$ .

Figure II.13. Schéma bloque d'une PLL.

La configuration de boucle à verrouillage de phase que nous venons de présenter ne fait que reproduire le signal  $f_{REF}$  à la sortie du VCO. Pour la génération de fréquences porteuses, ce circuit n'est pas d'une grande utilité car les signaux à l'entrée et à la sortie ont la même fréquence. Le système de boucle à verrouillage de phase illustre toute sa puissance lorsque des diviseurs de fréquence sont introduits dans la boucle. Ce qui nous permet de réaliser la fonction de synthèse de

fréquence, deux types d'architectures s'appuyant sur l'utilisation d'une telle boucle à verrouillage de phase, vont êtres étudiées par la suite : PLL à division entière ; et PLL à division fractionnaire [5].

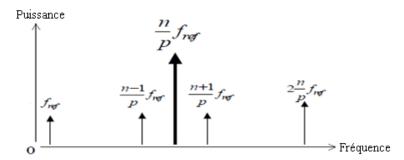

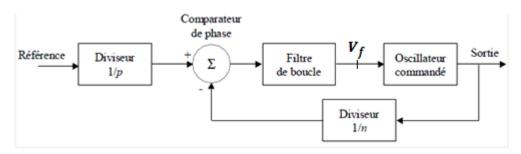

#### a. PLL à division entière

La boucle à verrouillage de phase à division entière est la plus simple structure de synthétiseur à PLL. Les diviseurs de fréquences sont en général des diviseurs numériques, qui divisent par un nombre entier, souvent programmable.

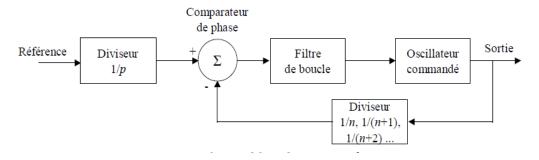

La chaîne directe d'une PLL typique (Figure II.14) est composée d'un diviseur de fréquences, d'un comparateur de phase, d'un filtre de boucle qui attaque un oscillateur commandé. Dans la chaîne de retour est présent un diviseur de fréquences.

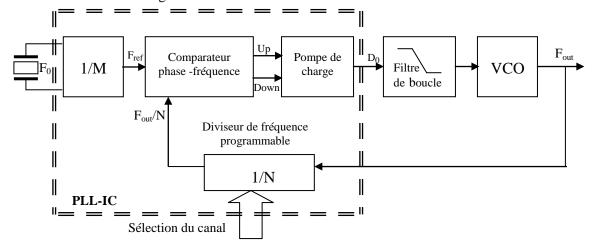

Figure II.14. Schéma-bloc d'une boucle à verrouillage de phase.

Les facteurs de division des diviseurs de fréquences, n et p, peuvent être des nombres entiers. Dans ce cas on a affaire à une PLL à division entière.

La fréquence de référence est d'abord divisée par p, ce premier diviseur programmable étant optionnel. En admettant que le diviseur de fréquence n soit totalement programmable, n pourra prendre des valeurs n, n + 1, n + 2, etc. On cherche alors l'écart entre deux fréquences consécutives. Cet écart est appelé le pas de fréquence, dans ce cas il est égal à :

$$\Delta f = \frac{f_{ref}}{p} [Hz] \tag{II.6}$$

En choisissant n, p et  $f_{ref}$  on peut donc élaborer une fréquence  $f_{sorti}$  qui sera un multiple non entier, de la fréquence  $f_{ref}$  et qui aura sa précision :

$$f_{sorti} = \Delta f. n = {n \choose p} f_{ref} [Hz]$$

(II.7)

La bande passante d'une PLL à division entière est directement proportionnelle à son pas de synthèse. En effet le filtre de boucle doit supprimer les composantes fréquentielles situées audessus de la fréquence de travail du comparateur de phase, afin de réduire la génération de raies parasites et d'assurer la stabilité de la boucle.

#### b. Synthétiseur à division fractionnaire

Pour contourner la difficulté crée par la dépendance de la bande passante de la PLL à son pas de synthèse, il est possible d'utiliser un diviseur de fréquences dont le facteur de division moyen est non entier. Le schéma de principe d'une telle boucle à verrouillage de phase est présenté à la figure II.15. Ici, la fréquence des signaux appliqués au comparateur de phase est très supérieure au pas de synthèse. La bande passante est donc plus importante que dans le cas de la PLL entière.

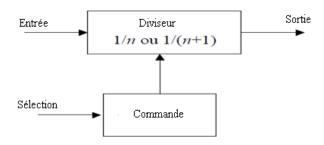

La division de fréquences non entière est usuellement réalisée par un diviseur de fréquences qui possède au moins deux facteurs de division. En commutant rapidement entre ces facteurs de division, selon une loi appropriée, il est possible de réaliser un facteur de division moyen fractionnaire et donc un faible pas de synthèse.

Figure II.15. Schéma-bloc d'une PLL fractionnaire.

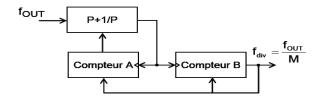

Le plus souvent on utilise un diviseur de fréquences possédant deux facteurs de division successifs, on parle alors de diviseur n/n+1 comme présenté à la figure II.16. Dans ce cas, la fréquence de sortie peut évoluer en n fois et n+1 fois la fréquence de référence. Le pas de synthèse est fixé par la commande du diviseur [5].

Figure II.16. Diviseur de fréquences fractionnaire.

Ce type de diviseur introduit une erreur de phase permanente, l'oscillateur de la PLL est alternativement en avance ou retard de phase, au rythme des commutations du facteur de division. La PLL fractionnaire génère donc potentiellement plus de raies parasites qu'une PLL entière. Pour minimiser la génération de raies parasites, il est donc nécessaire d'optimiser le filtre de boucle, pour obtenir une forte atténuation des hautes fréquences, et de choisir une bonne loi de commande pour le diviseur [5].

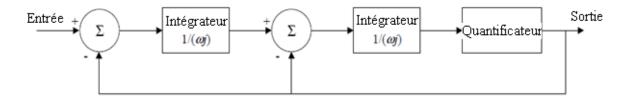

**Figure II.17.** Modulateur  $\sum \Delta$  d'ordre 2.

Souvent un modulateur Sigma-Delta (SD) est utilisé pour contrôler le facteur de division [29]. Ceux-ci génèrent un signal de commande pseudo-aléatoire, ressemblant à du bruit. De plus, le bruit des modulateurs SD d'ordre supérieur ou égal à deux est repoussé vers les hautes fréquences (Figure II.17), où il est relativement aisé de le supprimer grâce au filtre de boucle de la PLL. Les autres types de modulateurs, comme les systèmes à base de compteurs, ont, en général, l'inconvénient de générer des raies parasites d'amplitude élevée en raison de leur comportement plus périodique [5].

Dans la section précédente, nous avons considéré la boucle à verrouillage de phase comme l'élément fondamental de tout synthétiseur de fréquence indirect qui utilise son principe, et nous avons présenté deux classifications de la boucle: entière et fractionnaire. Afin de mieux appréhender le fonctionnement du système, il est nécessaire d'identifier le rôle de chacun de ces blocs constitutifs et de confronter les différentes solutions envisageables pour les concevoir.

#### II.6. Description des éléments constitutifs de la PLL

#### II.6.1. La source de référence

Le signal de référence  $f_o$  doit posséder des caractéristiques élevées en terme de stabilité. Il est délivré par un oscillateur à cristal, généralement un quartz. C'est sur cette fréquence de référence que le signal de sortie de la PLL va se synchroniser [9], [29].

#### II.6.2. Comparateur de phase

Le comparateur de phase compare les phases de la référence et la phase du VCO à travers le diviseur et génère un signal de sortie  $V_d$  proportionnel à un coefficient  $K_d$  appelé transconductance du comparateur de phase [5].

$$V_D(t) = K_D[\varphi_i(t) - \varphi_0(t)]$$

(II.8)

Le comparateur de phase peut être réalisé de manière analogique (mélangeur, ...) ou numérique (machine d'état, portes XOR, bascules JK, ...).

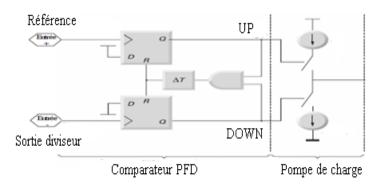

Le comparateur le plus utilisé est la machine à trois états. Ce comparateur numérique est appelé détecteur de phase-fréquence (Phase Frequency Detector (PFD)). En effet ce type de comparateur quand il est associé à une pompe de charges, permet d'atteindre une très large plage d'accrochage. Celle-ci est approximativement égale à la plage de fréquences couverte par